# **Ulf Schwalbe**

# Vergleichende Untersuchungen dreistufiger Schaltnetzteiltopologien im Ausgangsleistungsbereich bis 3 kW

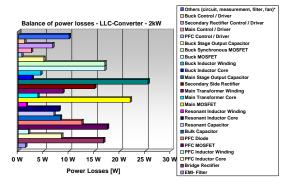

ISBN 978-3-938843-49-9 urn:nbn:de:gbv:ilm1-2009000330

# Vergleichende Untersuchungen dreistufiger Schaltnetzteiltopologien im Ausgangsleistungsbereich bis 3 kW

#### Dissertation

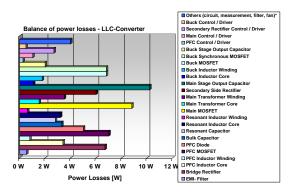

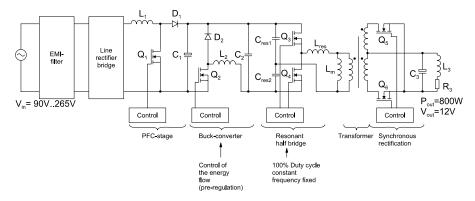

# zur Erlangung des akademischen Grades

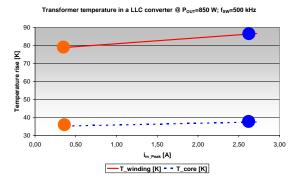

# **Doktoringenieur** (Dr.-Ing.)

vorgelegt der

Fakultät für Elektrotechnik und Informationstechnik

der Technischen Universität Ilmenau

von

Dipl.-Ing. Ulf Mario Schwalbe

geb. am 13.11.1978 in Erfurt

vorgelegt am: 11.11.2008

Gutachter: 1. Prof. Dr.-Ing. habil. Jürgen Petzoldt

2. Prof. Dr. Johann Walter Kolar

3. Dr. Gerald Deboy

Verteidigung am: 14.09.2009

urn:nbn:de:gbv:ilm1-2009000330

ISBN 978-3-938843-49-9

für meine Tochter Louise und in Gedenken an meinen Vater Reimund

So eine Arbeit wird nie fertig. Man muss sie für fertig erklären, wenn man nach Zeit und Umständen das Mögliche getan hat.

Johann Wolfgang von Goethe "Italienreise" (1787)

#### Vorwort

Die vorliegende Arbeit entstand während meiner Tätigkeit als Forschungsstudent an der Technischen Universität Ilmenau im Fachgebiet "Leistungselektronik und Steuerungen in der Elektroenergietechnik" der Fakultät für Elektrotechnik und Informationstechnik. Die Bearbeitung der Aufgabe erfolgte in enger Zusammenarbeit mit der ISLE GmbH in Ilmenau und der Infineon Technologies Austria AG in Villach.

Mein besonderer Dank gilt Herrn Professor Dr.-Ing. habil. Jürgen Petzoldt, Leiter des Fachgebietes "Leistungselektronik und Steuerungen in der Elektroenergietechnik", für die vielen hilfreichen fachlichen Diskussionen und Anregungen, die Begutachtung der Dissertationsschrift sowie der wissenschaftlichen Gesamtbetreuung der Arbeit.

Des Weiteren möchte ich mich bei Herrn Dr. Gerald Deboy von der Infineon Technologies Austria AG für die weitreichende Unterstützung bedanken, die diese Dissertation erst möglich gemacht haben.

Mein besonderer Dank gilt Herrn Dr.-Ing. Tobias Reimann sowie Herrn Dipl.-Ing. Marko Scherf von der ISLE GmbH für ihre wegweisende Begleitung meines wissenschaftlichen Werdegangs, ihre Motivation sowie die vielfältigen Anregungen und Unterstützungen. Durch ihr Wirken haben sie maßgeblich zum Gelingen dieser Arbeit beigetragen.

Besondere Anerkennung gilt Herrn Professor Dr.-Ing. habil. Wolfgang Gens für die wertvollen Anregungen in der Entstehungsphase dieser Dissertation.

Bei allen Kolleginnen und Kollegen des Fachgebiet "Leistungselektronik und Steuerungen in der Elektroenergietechnik" der TU Ilmenau, der ISLE GmbH und der Infineon Technologies Austria AG, die mir während meines Forschungsstudiums in irgendeiner Form behilflich waren und somit zum Gelingen der Arbeit beitrugen, möchte ich mich an dieser Stelle bedanken. Gleiches gilt auch für die Studenten, die im Rahmen ihrer Studien- und Diplomarbeiten wertvolle Beiträge zur behandelten Thematik geliefert haben.

Für die mit großer Sorgfalt und Mühe durchgeführte redaktionelle Bearbeitung der Dissertationsschrift bedanke ich mich bei Frau Dipl.-Ing. Elke Schöne.

Für die materielle und ideelle Unterstützung meines Forschungsthemas seitens der Industrie danke ich stellvertretend Herrn Dr. Gerald Deboy und Herrn Dr. Lutz Görgens von der Infineon Technologies Austria AG.

Nicht zuletzt bedanke ich mich recht herzlich bei meinen Eltern Christel und Reimund, meiner Partnerin Anja und bei meinem sehr guten Freund Oskar Schneider für die moralische Unterstützung.

Ulf Schwalbe

Erfurt, den 04.11.2008

#### Abstract

Switch mode power supplies (SMPS) are well established in our modern world. Their main advantages are the realization of high efficiency and energy saving potential. Another benefit and design objective is a high power density to reach lightweight systems of small size.

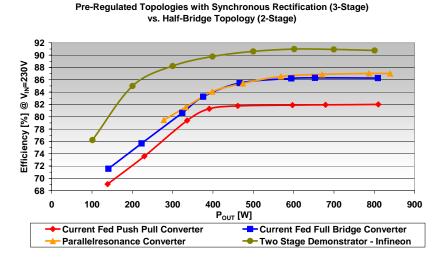

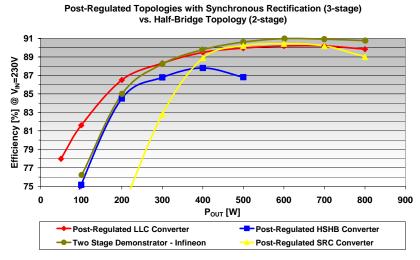

This thesis focuses on the benefits and the challenges of three stage DC-DC converters in SMPS applications. They are compared to state-of-the-art two stage DC-DC converters for high power and low output voltages. Possibilities for improvement of technical and miscellaneous parameters should be shown.

The obtained information refers to power supply systems with maximum input power of 3680 W. This is the maximum power of a 230 V single phase supply with a 16 A fuse. The main applications are server and telecommunication AC-DC power supplies.

Due to the complexity of SMPSs all investigations in this work have a mainly experimental background. Theoretical descriptions and calculations would require large simplifications of the real system. Thus, gained results would become inaccurate. Simulations and calculations are used during the practical implementation.

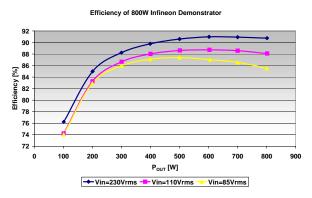

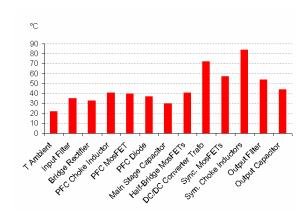

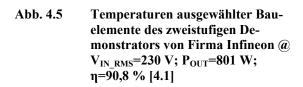

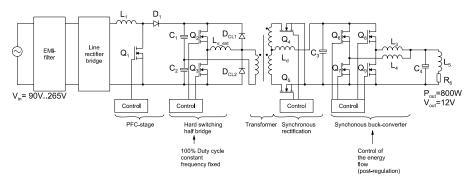

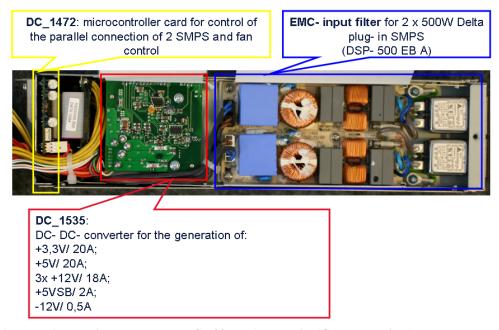

Six SMPS demonstrators were developed during this dissertation work. All these systems were designed with the same specification i.e. for 12 V output voltage and 800 W output power. As a comparison an 800 W two stage power supply from Infineon Technologies AG was used.

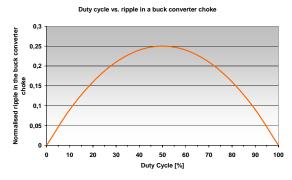

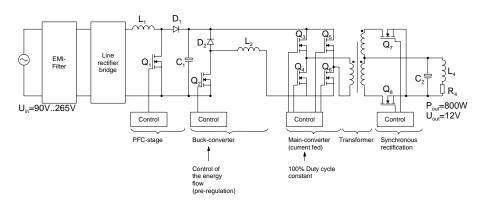

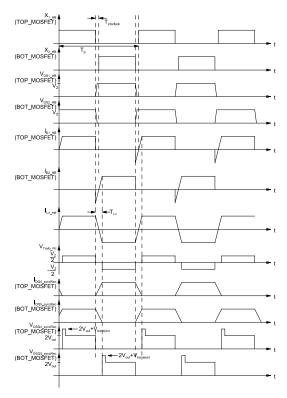

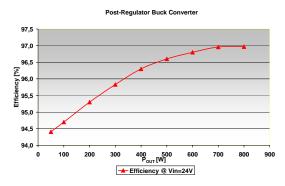

Three stage solutions can overcome the trade-offs in two stage power supplies. The optimization problem in a two stage SMPS is to find a compromise between the bulk capacitor size (cost) and the design of the DC-DC converter regarding the input voltage range. Three stage power supplies use an extra stage to decouple the output power regulation from the main stage. The main stage operates like a DC transformer. This stage can be optimized for operation at a 100 % duty cycle. Furthermore this is a good basis for zero voltage switching (ZVS) or resonant switching respectively. The extra stage can be implemented as a simple highly efficient buck converter which can easily cope with the wide input voltage range.

There are two ways to arrange the buck stage. One possibility is on the primary side of the transformer in a pre regulated concept. Here the buck converter supplies the main stage with a constant voltage. Another possibility is an arrangement on the secondary side of the main stage in a post regulated concept. The DC transformer stage transfers the bulk voltage with all variations to the secondary side. The following buck stage has to maintain a constant output voltage.

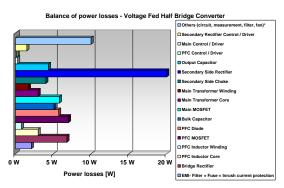

The two stage demonstrator is a voltage fed, hard switching half bridge with power factor correction (PFC) stage.

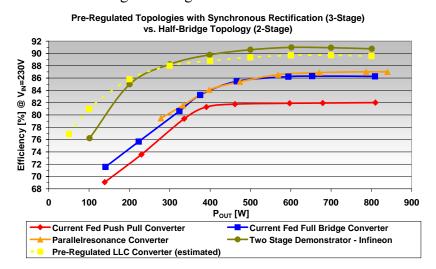

The following pre regulated three stage powers supplies were investigated: current fed push pull converter, current fed full bridge converter and a current fed parallel resonant converter. The research of post regulated three stage SMPSs concentrates on: hard switching half bridge, serial resonant converter and an LLC converter. All three stages operate with a PFC stage. The main results of this dissertation are summarised below.

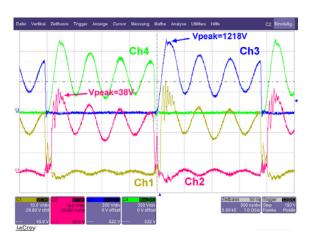

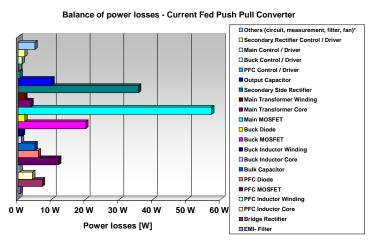

The following characteristics apply to pre regulated switch mode power supplies: The main primary side MOSFETs in the current fed push pull converter and in the current fed full

bridge converter are stressed with high voltages. However, the secondary side rectifier MOS-FETs in all current fed systems operate with low voltage stress.

The current fed parallel resonant converter is a modification of the current fed full bridge converter to achieve low switching losses in resonant mode operation. The stress on the active components is analogue to the full bridge converter. A drawback of this solution is the load dependent resonant and transfer behaviour.

The implementation of synchronous rectification control in these current fed systems needs some effort. Self driven circuits were not sufficient.

A topology with a current fed main stage is not adequate for the generation of high currents and low output voltages. The main reason for this is the high stress on the active components due to the leakage inductance in the system.

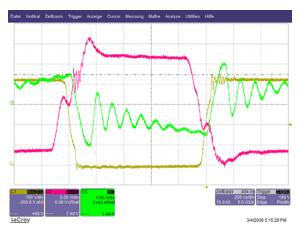

Post regulated power supplies are characterised by the following facts: The investigation on the hard switching half bridge revealed load dependent transfer behaviour. Therefore this converter is unsuitable for a DC transformer application. Furthermore a limitation choke for the current rise and clamping diodes was necessary to achieve ZVS and low voltage stress on the secondary side rectifiers. Also, due to the occurring voltage drop the limitation choke reduces the converter output power.

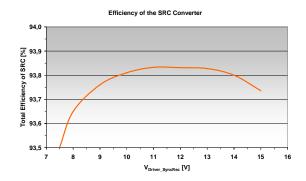

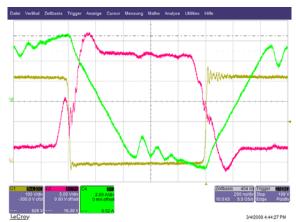

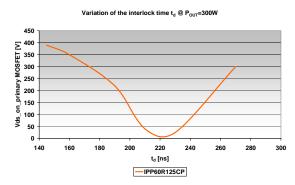

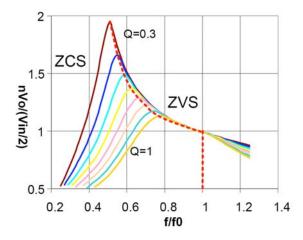

The serial resonant converter is suitable as a DC transformer in high output power applications. The load current is used to charge the output capacitances of the MOSFETs to achieve ZVS condition. The ZVS condition is lost at light load operation, influenced by the switching frequency, interlock time and the angle of switching. If the ZVS condition is lost, the primary MOSFETs in the resonant converter operate in hard switching mode with high switching losses.

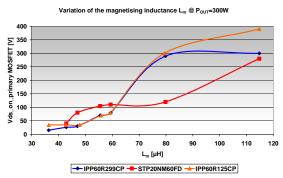

A modified serial resonant topology, the LLC converter, solves the problem of losing ZVS at light load operation. ZVS condition is supported by the transformer magnetising current which is independent of the load current. ZVS condition can be achieved over a wide operation range to limit losses in the primary side MOSFETs. The LLC converter is a real load independent DC transformer. This is a major result of this research.

The main advantage of a three stage solution compared to a two stage power supply is the reduction of the bulk capacitance. The voltage variation at the bulk capacitor during a brownout is regulated with a simple buck converter. The reduced bulk capacitance leads to cost savings and a gain in power density. The galvanic isolation and the output regulation is separated in a three stage concept, therefore the design of the stages is quite simple.

Every stage can operate independently, therefore the system gains degrees of freedom. More freedom in design leads to a better adjustment between three stage SMPS and application.

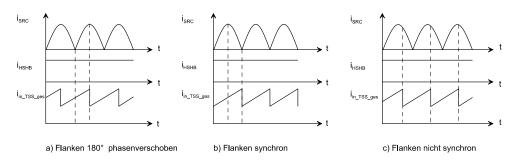

If required, a synchronisation between the stages can be implemented. The load current of the bulk capacitor can be reduced by synchronising the PFC stage and the following stage in high power system.

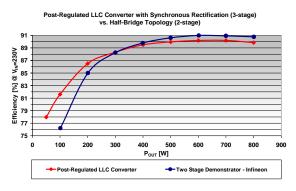

Normally, the design of the different stages in a three stage SMPS is quite simple, because of the spreading of the output power regulation and the galvanic isolation to different stages. This separation could be used in a three stage LLC converter to reach a gain in efficiency compared to a two stage setup.

The possibility for discrete optimisation of the stages leads to an optimised SMPS system.

The main drawback of a three stage solution is the higher component count, compared to a two stage supply. However, higher component count and system costs do not correlate directly. A practical comparison between the investigated power supplies showed a similar cost level.

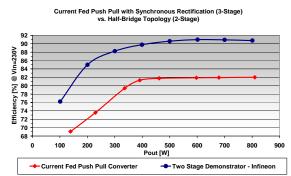

The major goal of the thesis, to achieve a gain in efficiency with three stage SMPSs compared to a two stage solution, was not reached completely. The main reason is the high switching frequency in the different stages. High switching frequency leads to high switching losses in the switches.

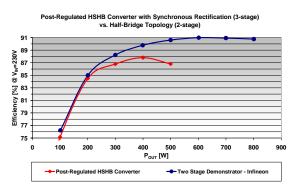

At full load operation the efficiency of the three stage LLC converter was less than in the two stage SMPS. However, at light load the situation reversed. The three stage LLC converter reached higher efficiency than the two stage SMPS.

Due to the reduction of bulk capacitor size, an improvement of power density was reached with three stage solutions, compared to two stage SMPSs.

This investigation highlights the qualitative properties of the different topologies. All quantitative statements in this work refer to current state-of-the-art semiconductors and passive components. Due to the permanent development in these fields all conclusions are only indicative.

In this research currently common switching frequencies have been proven. Therefore, the efficiency values show not the maximum values for these topologies. A reduction of the switching frequency would lead to a gain in total efficiency. By using state-of-the-art semi-conductors and passive components, switching frequencies of about 70 kHz to 130 kHz are optimal for achieving high efficiency.

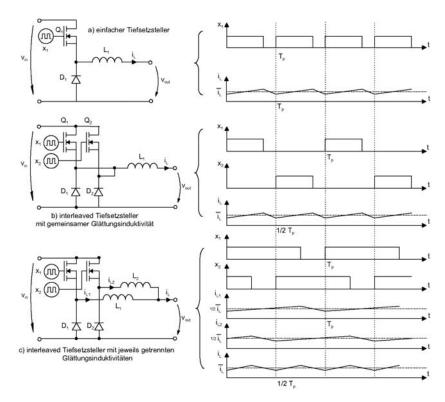

For high output power interleaved topologies in combination with low switching frequencies (70 kHz to 130 kHz) are reasonable. Cancellation effects caused by control can be used to reduce passive components stress in these topologies.

It became clear that the LLC converter with secondary side buck converter is the best three stage solution. Due to the excellent properties in a three stage solution the combination of an LLC converter with a primary side buck stage is reasonable, too. This setup would facilitate the design of the buck regulator stage. This configuration could be investigated in ongoing research. An efficiency estimation is already given in this thesis.

# Inhaltsverzeichnis

| 1. I        | Einleit | ung                                                                 | 1  |

|-------------|---------|---------------------------------------------------------------------|----|

| 2. (        | Grund   | lagen und Stand der Technik                                         | 5  |

| 2.1         | Gr      | undlagen der Schaltnetzteiltechnik                                  | 5  |

| 2.2         | Sta     | and der Technik                                                     | 7  |

| <b>3.</b> A | Analys  | e des Optimierungspotentials und Zielstellung der Arbeit            | 15 |

| 3.1         | Vo      | orbemerkungen                                                       | 15 |

| 3.2         | Le      | istungshalbleiter                                                   | 15 |

| 3           | 3.2.1   | Vorbemerkungen                                                      | 15 |

| 3           | 3.2.2   | Hochvolt-Silizium (Si)-Leistungs-MOSFETs                            | 15 |

| 3           | 3.2.3   | Niedervolt-Silizium (Si)-Leistungs-MOSFETs                          | 22 |

| 3           | 3.2.4   | Siliziumkarbid (SiC)-Schottky-Dioden                                | 28 |

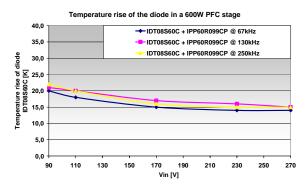

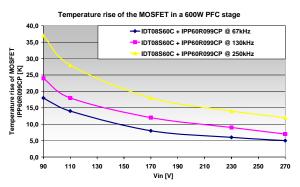

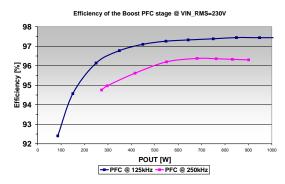

| 3           | 3.2.5   | Vergleich von Si- und SiC-Dioden in einer Hochsetzsteller-PFC-Stufe | 31 |

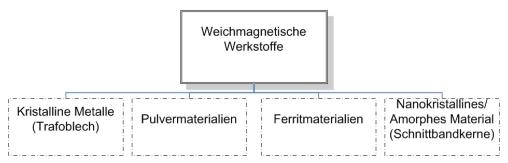

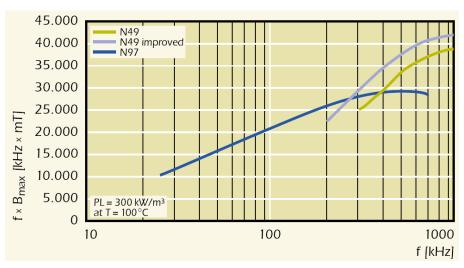

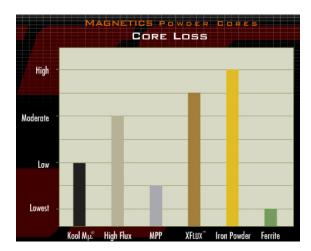

| 3.3         | Ma      | agnetwerkstoffe für Schaltnetzteilanwendungen                       | 34 |

| 3.4         | Sc      | haltnetzteiltopologien im Überblick                                 | 37 |

| 3           | 3.4.1   | Vorbemerkungen                                                      | 37 |

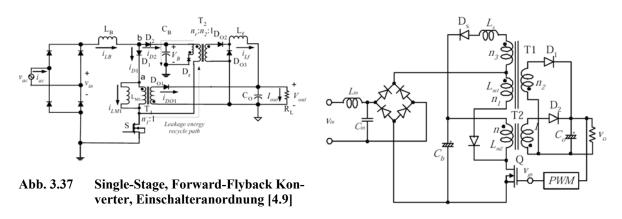

| 3           | 3.4.2   | Einstufige Topologien (Single-Stage)                                | 38 |

| 3           | 3.4.3   | Zweistufige Topologien (Dual-Stage)                                 | 39 |

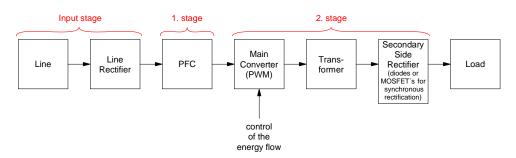

| 3           | 3.4.4   | Dreistufige Topologien (Three-Stage)                                | 41 |

| 3.5         | Po      | wer Factor Correction (PFC)-Stufe                                   | 42 |

| 3           | 3.5.1   | Vorbemerkungen                                                      | 42 |

| 3           | 3.5.2   | Boost-PFC-Stufe                                                     | 44 |

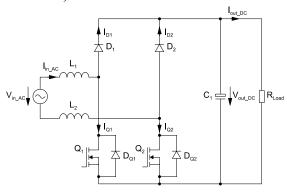

| 3           | 3.5.3   | Bridgeless-PFC-Stufe                                                | 50 |

| 3           | 3.5.4   | Zusammenfassung und Schlussfolgerungen                              | 52 |

| 3.6         | На      | uptwandler-Stufe                                                    | 53 |

| 3           | 3.6.1   | Vorbemerkungen                                                      | 53 |

| 3           | 3.6.2   | Partiell hart schaltende Wandler                                    | 54 |

| 3           | 3.6.3   | Resonanzwandler für die DC-DC Transformation                        | 57 |

| 3           | 3.6.4   | Zusammenfassung und Schlussfolgerungen                              | 67 |

| 3.7         | Se      | kundärseitige Gleichrichter                                         | 68 |

| 3.8         | Pa      | rtiell hart schaltende und resonante Ansteuerung von MOSFETs        | 73 |

| 3           | 3.8.1   | Partiell hart schaltende Ansteuerung                                | 73 |

| 3           | 3.8.2   | Resonante Ansteuerung                                               | 77 |

| 3           | 3.8.3   | Ergebnisse der Untersuchungen zur Ansteuerung von MOSFETs           | 79 |

| 3.9   | Unt     | ersuchungen zur Synchronisation verschiedener Schaltnetzteilstufen                | 80  |

|-------|---------|-----------------------------------------------------------------------------------|-----|

| 3.9   | 9.1     | Vorbemerkung                                                                      | 80  |

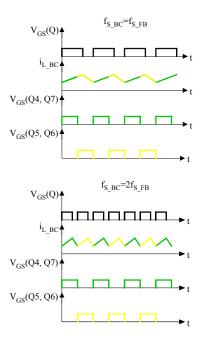

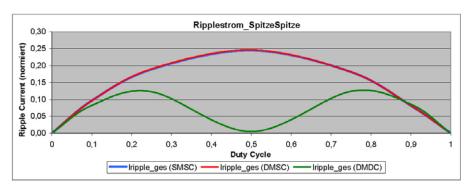

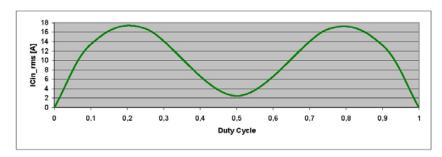

| 3.9   | 9.2     | Synchronisation von PFC-Stufe und Hauptwandler                                    | 80  |

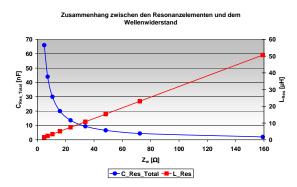

| 3.9   | 9.3     | Synchronisation von Resonanz- und partiell hart schaltenden Wandlern              | 83  |

| 3.9   | 9.4     | Ergebnisse der Untersuchungen zur Stufensynchronisation                           | 85  |

| 3.10  | Zie     | Istellung der Arbeit und Vorgehensweise                                           | 86  |

| 4. Zv | weistu  | fige Schaltnetzteiltopologien                                                     | 89  |

| 4.1   | Vor     | bemerkungen                                                                       | 89  |

| 4.2   | Par     | tiell hart schaltender Halbbrücken-Konverter                                      | 89  |

| 4.2   | 2.1     | Topologie, Parameter und Realisierung                                             | 89  |

| 4.3   | 2.2     | Ergebnisse der Betrachtungen                                                      | 90  |

| 4.3   | Erg     | ebnisse der Untersuchungen an zweistufigen Schaltnetzteilen                       | 91  |

| 5. Di | reistuf | ige Schaltnetzteiltopologien                                                      | 93  |

| 5.1   | Vor     | bemerkungen                                                                       | 93  |

| 5.2   | Prir    | närseitig geregelte (Pre-Regulated) Schaltnetzteile                               | 93  |

| 5.2   | 2.1     | Vorbemerkungen                                                                    | 93  |

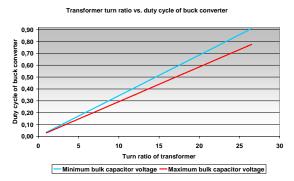

| 5.2   | 2.2     | Topologieauswahl für Pre-Regulated Schaltnetzteile                                | 94  |

| 5.2   | 2.3     | Current Fed Push Pull-Konverter                                                   | 96  |

| 5.2   | 2.4     | Current Fed Full Bridge-Konverter                                                 | 100 |

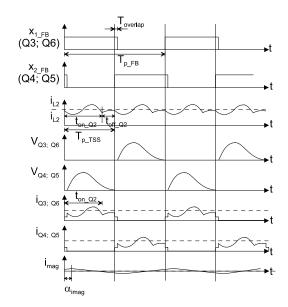

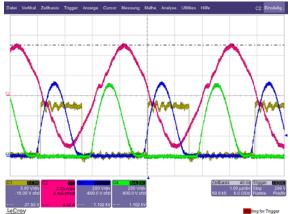

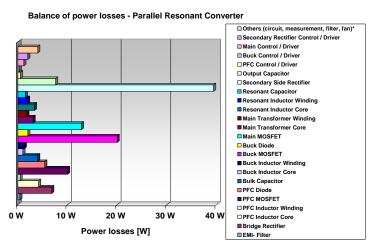

| 5.2   | 2.5     | Parallelresonanzkonverter                                                         | 104 |

| 5.2   | 2.6     | Betrachtungen zur Synchrongleichrichtung in stromgespeisten Systemen.             | 108 |

| 5.2   | 2.7     | Einfluss der Wandlerauslegung auf die Überspannungen im System                    | 109 |

| 5.2   | 2.8     | Parasitäre Elemente in Pre-Regulated Schaltnetzteilen                             | 110 |

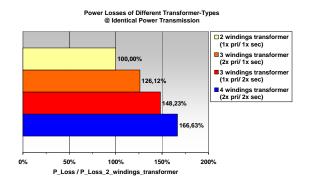

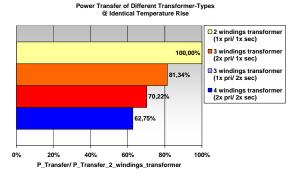

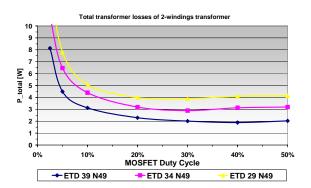

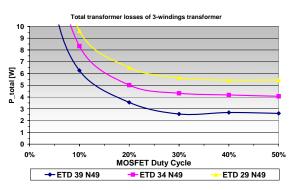

| 5.2   | 2.9     | Transformatoren in Pre-Regulated Schaltnetzteilen                                 | 111 |

| 5.2   | 2.10    | Ergebnisse der Untersuchungen an Pre-Regulated Schaltnetzteilen                   | 112 |

| 5.3   | Sek     | undärseitig geregelte (Post-Regulated) Schaltnetzteile                            | 116 |

| 5     | 3.1     | Vorbemerkungen                                                                    | 116 |

| 5     | 3.2     | Vergleich verschiedener Topologien für Post-Regulated Schaltnetzteile             | 116 |

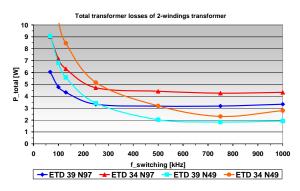

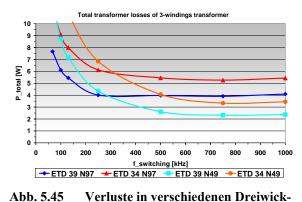

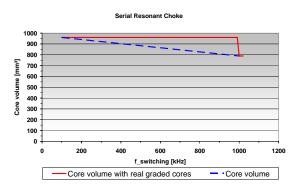

| 5     | 3.3     | Passive Bauelemente in der Hauptstufe                                             | 119 |

| 5     | 3.4     | Topologieauswahl für Post-Regulated Schaltnetzteile                               | 121 |

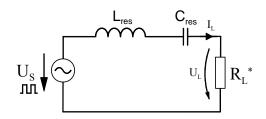

| 5     | 3.5     | Serienresonanzkonverter mit sekundärseitigem Tiefsetzsteller                      | 126 |

| 5     | 3.6     | LLC-Konverter mit sekundärseitigem Tiefsetzsteller                                | 130 |

| 5     | 3.7     | Partiell hart schaltende Halbbrücke mit sekundärseitigem Tiefsetzsteller          | 136 |

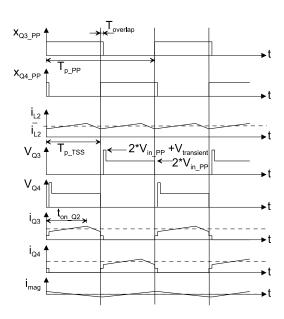

| 5     | 3.8     | Einflussfaktoren auf das Schaltverhalten des Serienresonanzkonverters             | 141 |

| 5     | 3.9     | Einflussfaktoren auf das Schaltverhalten der partiell hart schaltenden Halbbrücke | 144 |

|     | 5.3.   | Ergebnisse der Untersuchungen an Post-Regulated Schaltnetzteilen                 | 146 |

|-----|--------|----------------------------------------------------------------------------------|-----|

| 6.  | Disl   | kussion der Ergebnisse                                                           | 151 |

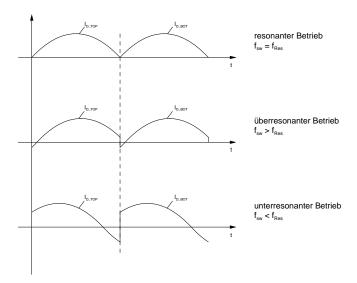

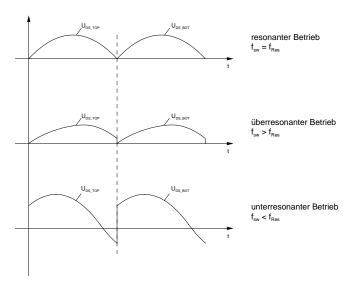

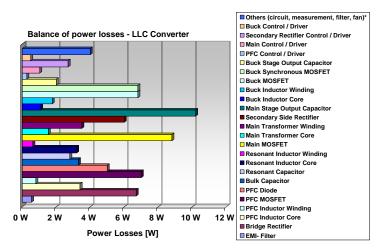

| (   | 5.1    | Betriebsarten des LLC-Konverters                                                 | 151 |

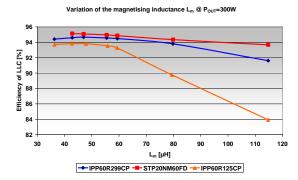

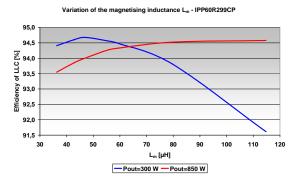

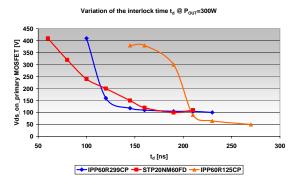

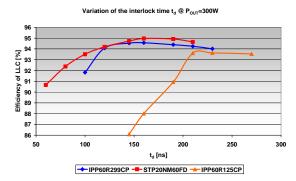

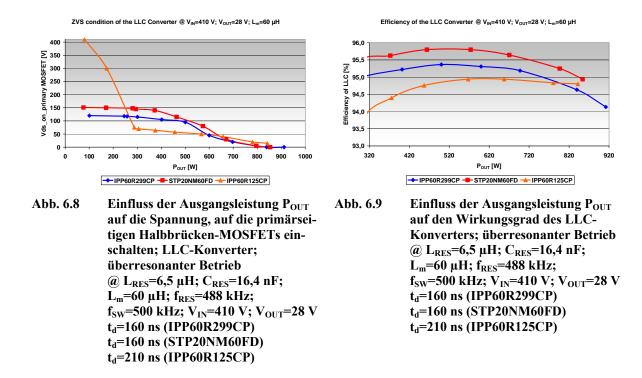

| (   | 5.2    | Einflussfaktoren auf das Schaltverhalten und den Wirkungsgrad des LLC-Konverters | 156 |

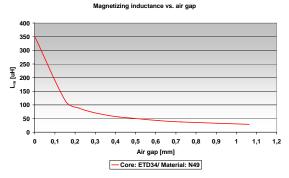

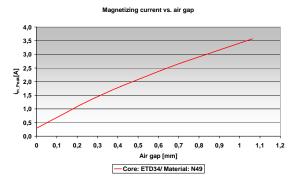

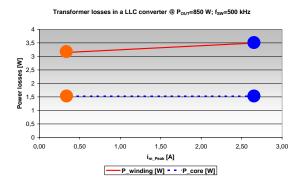

| (   | 5.3    | Einfluss des Luftspaltes auf die Verluste im Transformator des LLC-Konverters    | 162 |

| (   | 5.4    | Wirkungsgrad-Skalierung für einen 2 kW Post-Regulated LLC-Konverter              | 163 |

| (   | 5.5    | Diskussion eines Pre-Regulated LLC-Konverters                                    | 165 |

| (   | 5.6    | Ergebnisse der Untersuchungen zu dreistufigen Schaltnetzteiltopologien           | 167 |

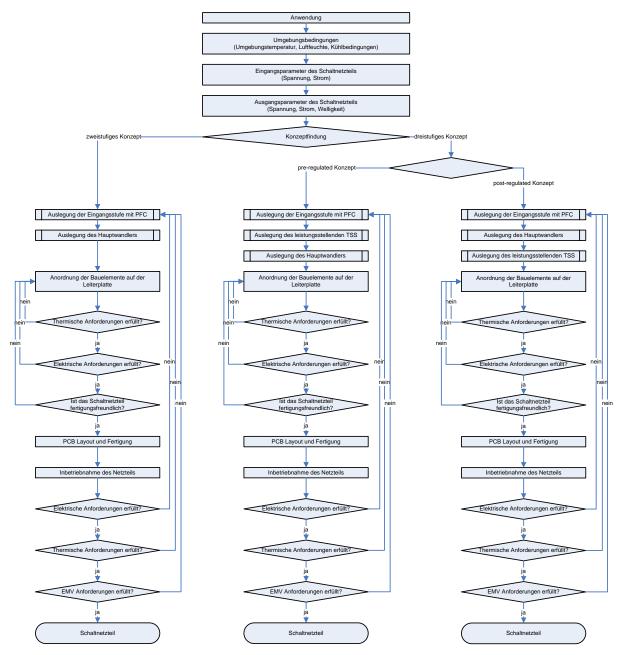

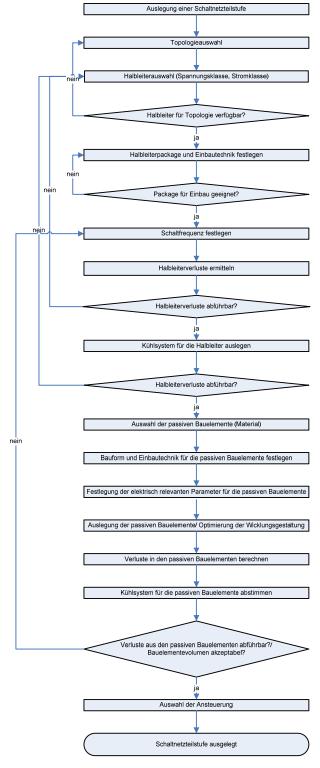

| (   | 5.7    | Entwurfssystematik für ein Schaltnetzteil                                        | 170 |

| 7.  | Zus    | ammenfassung und Ausblick                                                        | 173 |

| Lit | eratu  | rverzeichnis                                                                     | 177 |

| Ve  | rzeich | nis der Formelzeichen, Abkürzungen, Begriffe und Indizes                         | 183 |

| Δn  | hano   |                                                                                  | 192 |

# 1. Einleitung

Die Verkleinerung, die Gewichtseinsparung und die Wirkungsgrad-Erhöhung sind allgegenwärtige Trends in der Stromversorgungstechnik. Sie werden infolge der wachsenden Zahl von transportablen Geräten wie z.B. Handies, Laptops weiter forciert.

Traditionell gibt es zwei Arten von gesteuerten bzw. geregelten Stromversorgungen:

- lineare Spannungsregler

- getaktete Stromversorgungen (inkl. Schaltnetzteile)

Die Hauptunterschiede zwischen diesen beiden Arten bestehen in der Baugröße und dem Wirkungsgrad: Beim linearen Spannungsregler wird die von der angeschlossenen Last nicht benötigte Energie vom Regler verbraucht und somit für die Last eine geregelte Spannung zur Verfügung gestellt. Dies führt vor allem bei großen Unterschieden zwischen Ein- und Ausgangsspannung und hohen Lastströmen zu einem geringen Wirkungsgrad. Außerdem muss dafür gesorgt werden, dass die im Regler anfallende Wärme problemlos abgeführt werden kann. Aufgrund dieser Nachteile werden lineare Spannungsregler heute nur noch für sehr kleine Ausgangsleistungen (<10 W) eingesetzt.

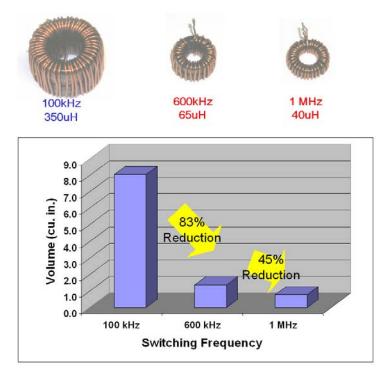

Im Vergleich dazu bieten getaktete Stromversorgungen die Möglichkeit einer im Idealfall verlustlosen Energieübertragung vom Eingang zum Ausgang. Das Wirkprinzip beruht auf der Steuerung des Energieflusses zur Last mithilfe ein oder mehrerer Schaltelemente, die per Pulsweitenmodulation (PWM) angesteuert werden. Hieraus ergibt sich gegenüber dem Linearregler auch die Möglichkeit einer Potenzialtrennung durch einen Transformator. Sowohl der Transformator als auch die nötigen passiven Bauelemente können mit zunehmender Pulsfrequenz kleiner gewählt werden [4.2]. Eine getaktete Stromversorgung wird als Schaltnetzteil bezeichnet, wenn sie einen Transformator zur Potentialtrennung besitzt.

Der Anteil von Schaltnetzteilen in der Stromversorgungstechnik hat in den letzten Jahren drastisch zugenommen. Die Stromversorgungen vieler Anwendungen, die zuvor linear geregelt wurden und über relativ schwere, großvolumige 50 Hz Transformatoren verfügten, wurden durch die leichteren und kostengünstigeren Schaltnetzteile ersetzt. Jeder Mobiltelefonbenutzer konnte diesen Trend in den letzten Jahren hautnah miterleben. Heute sind fast 100 % der Ladegeräte von Handies mit Schaltnetzteilen realisiert.

Der Hauptvorteil einer Switched Mode Power Supply (SMPS)-Lösung liegt in der Erzielbarkeit eines hohen Wirkungsgrades. Die Effizienz übertrifft konventionelle, linear geregelte Lösungen bei Weitem. Die Erhöhung des Wirkungsgrades führt zu einer Einsparung von Energie und fördert die Reduktion der weltweiten CO<sub>2</sub>-Emission, die in der heutigen Zeit sehr für erhitzte Gemüter sorgt.

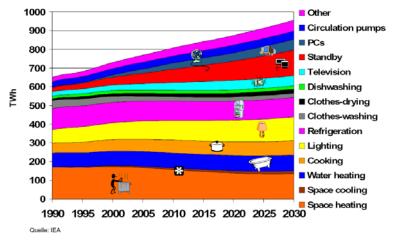

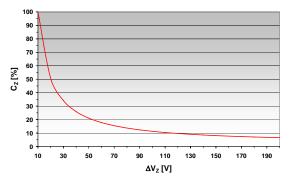

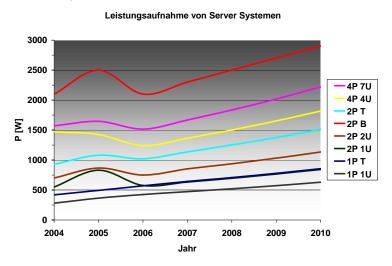

Ein Beispiel aus dem Bereich der Computeranwendung soll das Einsparpotential verdeutlichen: Bis zum Jahr 2011 wird es laut einer CPES Studie weltweit ca. 30 Mio. Server mit einer Durchschnittsleistung von 1200 W geben. Das führt zu einer Gesamtleistungsaufnahme von ca. 30 GW. Erhöht man den Wirkungsgrad dieser Server-SMPS um 1 % gegenüber dem derzeitigen Wert, so erreicht man eine Energieeinsparung von 360 MW. Dies entspricht der Leistung eines kleineren Kraftwerks, welches durch die Verbesserung der Effizienz eingespart werden könnte [1.3]. Solche Rechenbeispiele lassen sich auf viele Anwendungsfelder übertragen und zeigen das enorme Einsparpotential, das in den einzelnen Anwendungsfeldern steckt (Abb. 1.1).

Im Konsumgütermarkt, zum Beispiel, ist die Reduzierung der Standby-Verluste ein wichtiges Thema geworden. Durch den Einsatz von modernen Schaltnetzteilen kann in dieser Applikation eine Einsparung von ca. 90 % erreicht werden. Betrachtet man die ca. 200 Mio. Fernseh-

geräte, die in Europa vorhanden sind, so erzeugen diese eine Standby-Gesamtverlustleistung von 2 GW, wenn man 10 W Standby-Verluste pro Gerät veranschlagt.

Abb. 1.1 Energieeinsparungspotential durch Leistungselektronik in verschiedenen Anwendungsfeldern (Stand: 2005) [1.5]

Eine Reduktion der Standby-Verluste auf 1 W würde die Standby-Gesamtverluste auf 200 MW verringern [1.5]. Entwicklungen auf dem Gebiet der Leistungselektronik, die die Effizienz der Geräte steigern, sind dringend erforderlich, wenn man die Prognose zur Elektroenergieverbrauchsentwicklung bis zum Jahr 2030 betrachtet (Abb. 1.2). Die vorliegende Arbeit soll einen Beitrag zur Energieverbrauchs-, Gewichts- und Volumenreduzierung im Bereich der PC-Anwendungen, Server- und Telekomstromversorgungen leisten.

Abb. 1.2 Elektroenergieverbrauchsentwicklung für Geräte in Europa [1.1]

Im Bereich der Schaltnetzteilentwicklung gibt es mehrere Optimierungsziele. Die Optimierung des SMPS auf maximalen Wirkungsgrad bei maximaler Ausgangsleistung, auf geringe Standby-Verluste sowie die Optimierung auf Erzielung eines hohen Teillastwirkungsgrades. Speziell bei Server-Schaltnetzteilen ist der hohe Teillastwirkungsgrad eine gewachsene Anforderung. Server-Netzteile arbeiten heute meist in redundanten Systemen. Das bedeutet, zwei Netzteile teilen sich im Normalbetrieb die Leistung und geben jeweils 50 % ihrer max. Leistung ab. Bei Defekt eines Netzteils ist ein SMPS in der Lage, den Server weiter mit Energie zu versorgen. Dieses Beispiel verdeutlicht, dass die Anforderungen an die Schaltnetzteiltopologie abhängig von der Applikation sind.

Diese vorliegende Dissertation befasst sich mit der Untersuchung von dreistufigen Schaltnetzteiltopologien im Ausgangsleistungsbereich bis 3 kW. Diese Grenze ergibt sich infolge der Beschränkung der Untersuchungen auf SMPS am einphasigen Netz ( $V_{IN\_RMS}$ =230 V;  $I_{IN\_RMS}$ =16 A) zur Erzeugung einer potentialgetrennten DC-Spannung. Die typischen Applikationen auf die diese Arbeit abzielt, sind Stromversorgungen für Server, Telekommunikations-Server sowie Batterieladetechnik und Unterbrechungsfreie Stromversorgungen (USV).

Ein dreistufiges SMPS verfügt im Gegensatz zu einer zweistufigen Lösung über eine zusätzliche Wandlerstufe, die die Regulierung des Leistungsflusses von der Hauptstufe übernimmt. Die mit dreistufigen SMPS angestrebten Verbesserungen sind die Reduktion der Zwischenkreiskapazität und die damit verbundene Leistungsdichte-Erhöhung. Die Verbesserung des Systemwirkungsgrades mittels Aufteilung der Leistungsstellung und der galvanischen Trennung auf verschiedene Wandlerstufen. Die Erhöhung der Freiheitsgrade zur Beeinflussung von Schaltungsparametern und eine bessere Anpassung der dreistufigen Topologien an die jeweilige Anwendung.

Nach einigen Ausführungen zum Stand der Technik, der anhand von SMPS für Server dargestellt wird, folgen Betrachtungen zu Leistungshalbleitern und Magnetwerkstoffen. Im Anschluss daran wird detailliert auf Schaltungstopologien und die einzelnen Stufen eines Schaltnetzteils eingegangen. Es werden mögliche Ansatzpunkte zur Wirkungsgrad- bzw. Leistungsdichteerhöhung gezeigt.

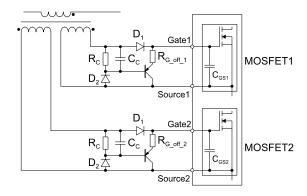

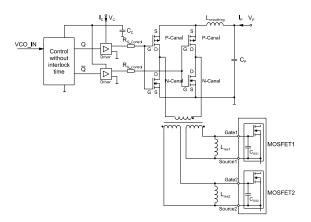

Untersuchungen zur resonanten und zur partiell hart schaltenden Ansteuerung von MOSFETs zeigen Möglichkeiten zur Reduktion von Ansteuerverlusten auf, insbesondere bei MOSFETs mit großen Chip-Flächen. Das Kapitel 3 zur Analyse des Optimierungspotentials schließt mit Betrachtungen zur Synchronisation von Schaltnetzteilstufen ab.

Aus der Analyse der Optimierungspotentiale leiten sich die Zielstellung der Arbeit und die Vorgehensweise ab. Im Anschluss ist das Kapitel 4 den zweistufigen Topologien gewidmet. Diese werden für die vergleichenden Untersuchungen mit den dreistufigen Topologien herangezogen. Kapitel 5 fasst alle Untersuchungen zu den dreistufigen SMPS zusammen. Es werden Schlussfolgerungen aus Simulationsergebnissen, Berechnungen und Messungen gezogen, die im folgenden Kapitel 6 für eine abschließende bewertende Diskussion wichtiger Ergebnisse benutzt werden.

# 2. Grundlagen und Stand der Technik

# 2.1 Grundlagen der Schaltnetzteiltechnik

Es gibt zwei Arten von getakteten Stromversorgungen, die transformatorlosen Topologien einerseits und die Schaltungskonzepte, die einen Transformator besitzen, andererseits.

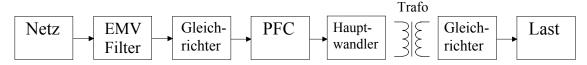

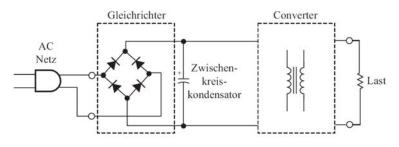

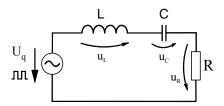

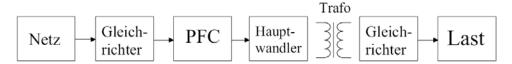

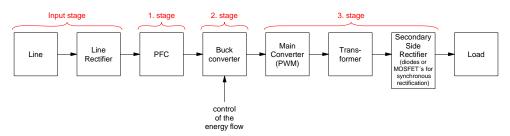

Zu den transformatorlosen Konzepten gehören alle Hochsetzsteller und Tiefsetzsteller sowie Hoch-Tiefsetzsteller. Besteht die Forderung nach einer Potentialtrennung, zwischen Netz und Last so ist der Einsatz eines Transformators unumgänglich. Alle Anordnungen, bei denen die Leistung über einen Transformator übertragen wird, werden als Schaltnetzteil bezeichnet (Abb. 2.1).

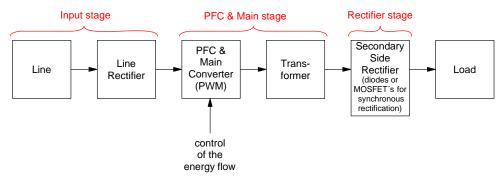

Abb. 2.1 Allgemeiner Aufbau eines zweistufigen Schaltnetzteils [7.2]

Der Einsatz eines Transformators bringt folgende Vorteile [4.2]:

- Die Ausgangsspannung ist gegenüber der Eingangsspannung elektrisch isoliert. Das erlaubt bei Bedarf eine Erdung der Ausgangsspannung.

- Bei Wahl eines entsprechenden Übersetzungsverhältnisses können Ein- und Ausgangsspannung in einem größeren Maße verschieden sein, als dies bei den Grundschaltungsarten ohne Transformator der Fall ist.

- Die durch minimales bzw. maximales Tastverhältnis vorgegebenen Grenzen im Stellbereich der Grundschaltungen ohne Transformator werden ausgeweitet.

- Mit mehreren Sekundärwicklungen unterschiedlicher Windungszahlen sind unterschiedliche galvanisch getrennte Ausgangsspannungen realisierbar.

Nachteile beim Einsatz eines Transformators [4.2]:

- Der Transformator liefert sowohl hinsichtlich des Gewichtes als auch des Volumens einen großen Anteil an den Gesamtsystemparametern.

- Der Magnetkreis und die nicht ideale Verkopplung zwischen den Windungen der Primär- und Sekundärseite verursachen Verluste.

- Die Streuinduktivität (Summe aus Transformator-Streuinduktivität und parasitärer Induktivität) sowie parasitäre Kapazitäten beeinflussen das Schaltverhalten der Leistungshalbleiter.

DC-DC Wandler mit Transformator können in Eintakt- und Gegentaktwandler unterteilt werden. Bei Eintaktwandlern wird der Transformator nur im ersten Quadranten des magnetischen Arbeitsbereiches betrieben. Das resultiert daraus, dass der Strom durch die Primärwicklung nur in einer Richtung fließen kann und daher auch die magnetische Feldstärke H nur eine Polarität besitzt. Der Transformator wird somit während der Einschaltdauer des Leistungshalbleiters aufmagnetisiert und im Rest der Schaltperiodendauer entmagnetisiert. Beim Gegentaktprinzip ermöglicht alternierendes Schalten von mindestens zwei Schaltern, die zusätzliche

Ausweitung des magnetischen Arbeitsbereiches des Transformators auf den dritten Quadranten der B-H-Kennlinie. Die Polarität des Stroms durch die Primärwicklung kann sich umkehren, der Magnetkreis aktiv entmagnetisiert und mit entgegengesetzter Polarität wieder aufmagnetisiert werden. Dies bedeutet unter der Prämisse, dass die Ummagnetisierungsverluste zunächst nicht betrachtet werden, eine erhebliche Steigerung der Ausnutzung des Magnetmaterials [4.2]. Weiterführende Grundbetrachtungen zu den Eintakt- und Gegentaktwandlern findet man in [1.2], [4.2].

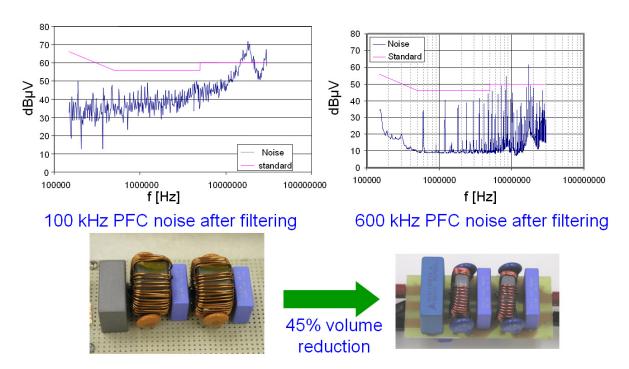

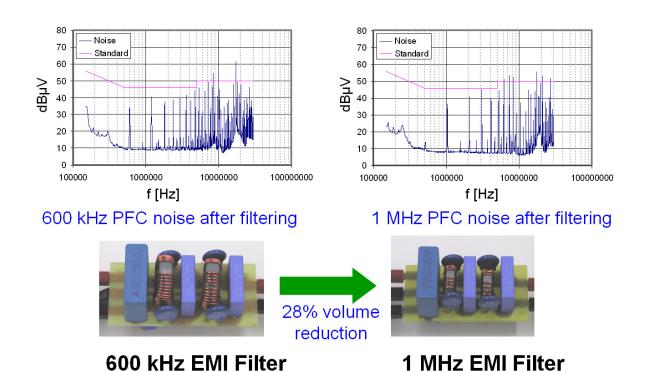

Der prinzipielle Aufbau eines zweistufigen SMPS ist in Abb. 2.1 zu sehen. Die Verbindung des Schaltnetzteils mit dem Stromnetz erfolgt über das Netzeingangsfilter. Dieses Filter hat die Aufgabe, die vom SMPS erzeugten Störungen (Elektromagnetische Verträglichkeit (EMV)) vom Netz fernzuhalten und das SMPS gegen Störungen aus dem Netz zu schützen. Die Erfüllung der EMV-Normen (EN 55014, EN 61000...) muss gewährleistet werden. In dem komplexen System Schaltnetzteil ist die Optimierung des EMV-Verhaltens ein weitreichendes Thema, das bei der Bauelementeauswahl beginnt, über das Printed Circuit Board (PCB)-Layout geht und bei der Optimierung der Schaltgeschwindigkeiten der Leistungshalbleiter endet. Das PCB-Layout bestimmt das spätere EMV-Verhalten des SMPS wesentlich.

Der Eingangsgleichrichter, der dem EMV-Filter folgt, ist eine der Schaltnetzteilkomponenten deren Weiterentwicklung in den vergangenen Jahren vernachlässigt wurde. Der Eingangsgleichrichter hat speziell bei niedriger Eingangsspannung ( $V_{IN\_RMS}$ =90 V) und dem damit verbundenen hohen Strom große Verluste.

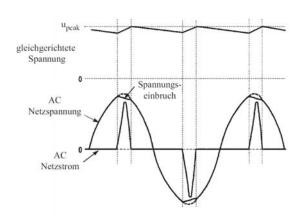

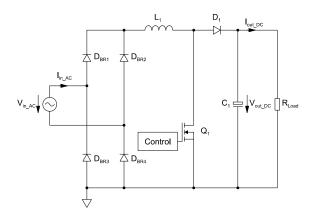

Mehr Aufmerksamkeit wurde hingegen der Power Factor Correction (PFC)-Stufe gewidmet. Ihre Aufgabe besteht darin, den Eingangsstrom des SMPS ( $i_{IN}$ ) mit der Netzspannung ( $v_{IN}$ ) in Phase zu bringen, und den Leistungsfaktor des Schaltnetzteils auf den Wert nahe Eins zu bringen. Die PFC-Stufe bewirkt, dass sich ein SMPS zum Netz hin wie ein ohmscher Widerstand verhält.

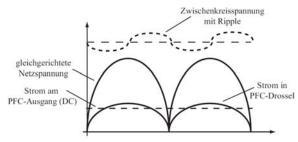

Da alle PFCs nach dem Hochsetzsteller-Prinzip bzw. Hoch-Tiefsetzsteller-Prinzip arbeiten, erzeugen sie unabhängig von der momentanen Eingangsspannung ( $v_{IN}$ ) eine konstante DC-Spannung, die von der folgenden Hauptwandler-Stufe verarbeitet wird. Der Hauptwandler eines zweistufigen SMPS schließt die galvanische Trennung, die Ausgangsspannung- bzw. Ausgangsstromregelung und den sekundärseitigen Gleichrichter mit ein. Nach dem sekundärseitigen Gleichrichter steht eine geregelte Ausgangsspannung für die Last zur Verfügung.

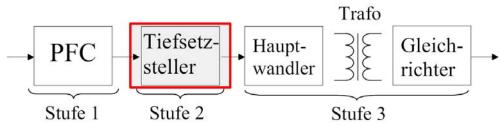

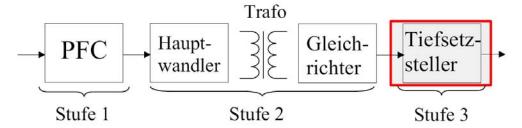

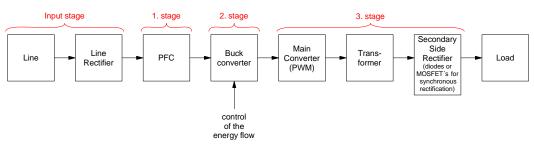

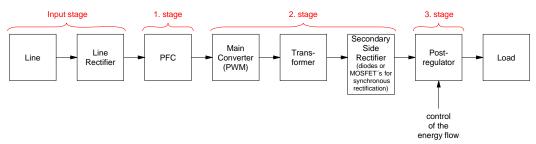

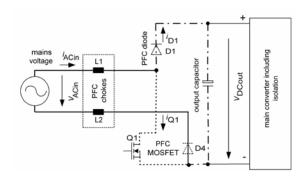

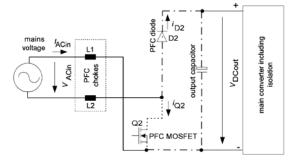

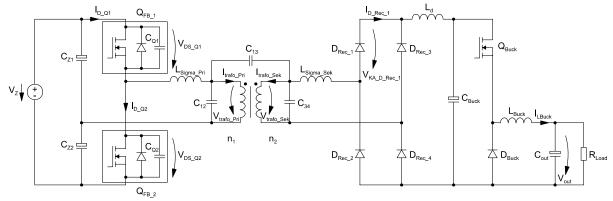

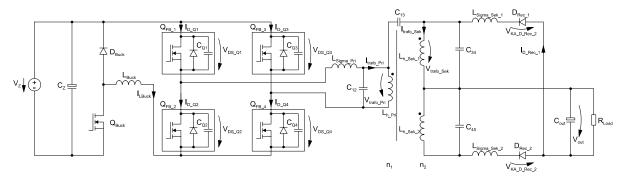

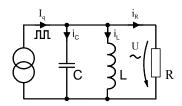

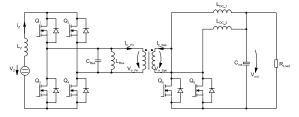

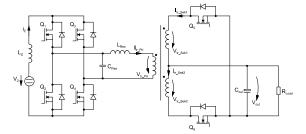

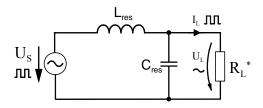

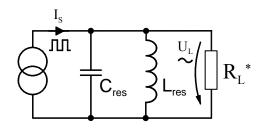

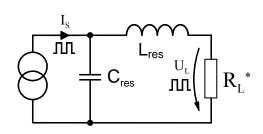

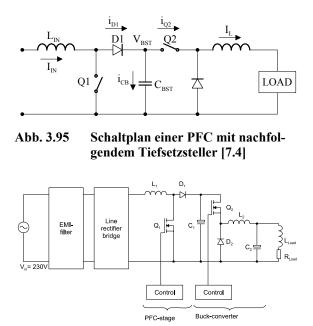

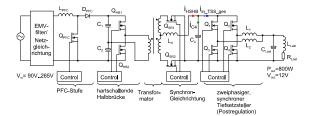

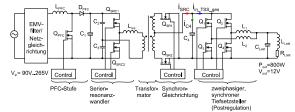

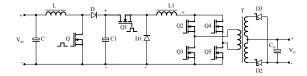

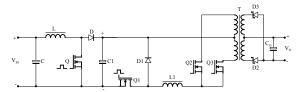

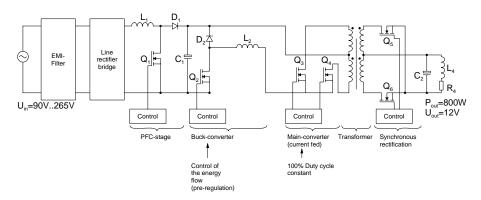

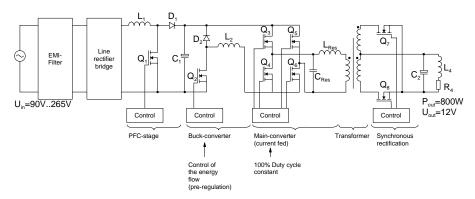

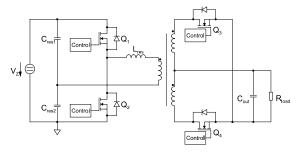

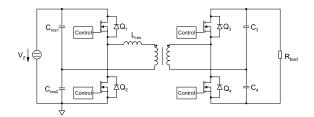

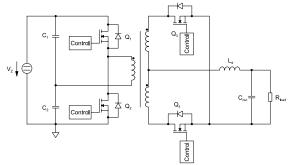

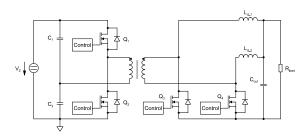

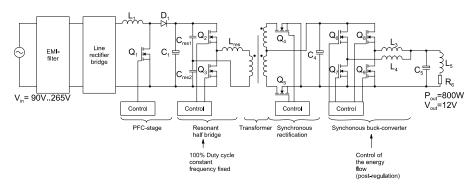

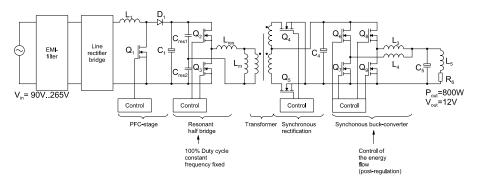

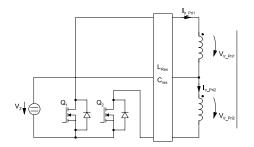

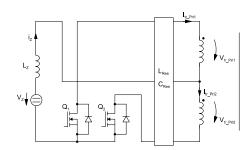

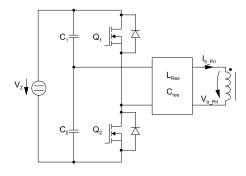

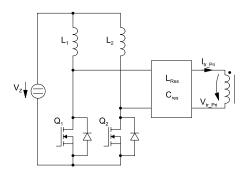

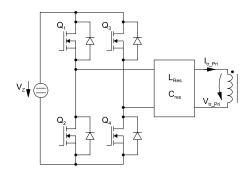

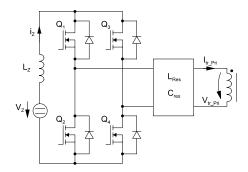

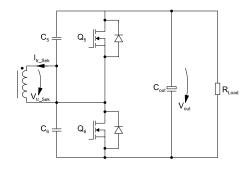

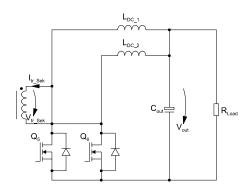

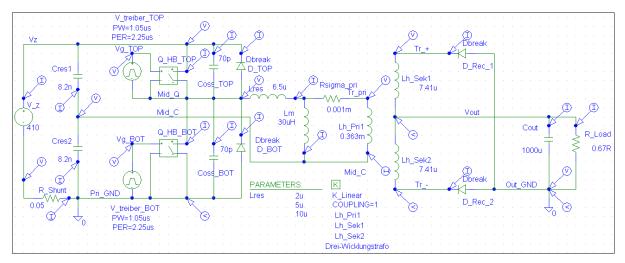

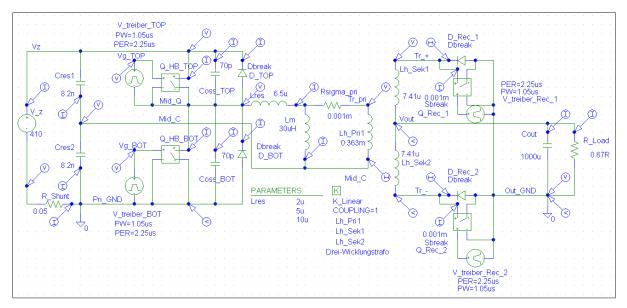

Diese Dissertation beschäftigt sich mit der Untersuchung von dreistufigen SMPS-Topologien. Ein dreistufiges SMPS verfügt im Gegensatz zu einer zweistufigen Lösung über eine zusätzliche Wandlerstufe, die die Regulierung des Leistungsflusses von der Hauptstufe übernimmt. Die Idee, die dieser Topologiefamilie zu Grunde liegt, ist die Optimierung der verschiedenen Wandlerstufen und damit die Erhöhung der Leistungsdichte bzw. des Systemwirkungsgrades. Es gibt zwei Arten der Ausführung: die primärseitig geregelten, die im Nachfolgenden als Pre-Regulated SMPS (Abb. 2.2) bezeichnet werden und die sekundärseitig geregelten, auch Post-Regulated SMPS (Abb. 2.3) genannt. Diese Ausführungen werden detailliert vorgestellt.

Abb. 2.2 Aufbau eines dreistufigen Schaltnetzteils mit primärseitiger Regelung durch einen Tiefsetzsteller (auszugsweise Darstellung) [7.2]

Abb. 2.3 Aufbau eines dreistufigen Schaltnetzteils mit sekundärseitiger Regelung durch einen Tiefsetzsteller (auszugsweise Darstellung) [7.2]

Diese Vorbetrachtungen sollten nur eine kurze Einführung in die Thematik Schaltnetzteil geben. Die folgenden Kapitel dieser Arbeit werden sich vertiefend mit PFC-Stufen, Hauptwandlern (partiell hart schaltend, resonant) und sekundärseitigen Gleichrichterstufen beschäftigen. Die EMV von Schaltnetzteilen ist nur ein Randthema dieser Arbeit.

#### 2.2 Stand der Technik

Die Analyse zum Stand der Technik ist in zwei Teilabschnitte gegliedert. Im ersten Teil werden experimentelle Untersuchungen von drei Schaltnetzteilen vorgestellt und im Bezug auf den Stand der Technik bewertet. Im nachfolgenden Abschnitt werden relevante Literaturstellen zum Thema dreistufiger Schaltnetzteiltopologien ausgewertet.

#### Praktische Analyse des Standes der Technik

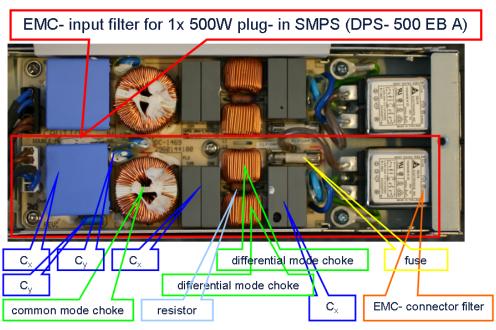

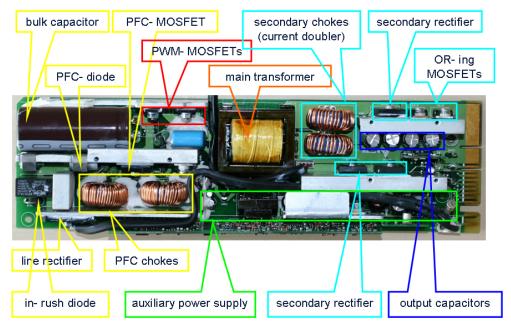

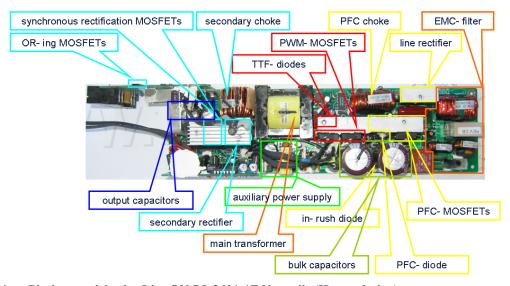

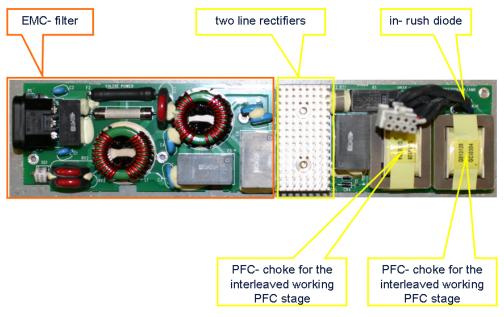

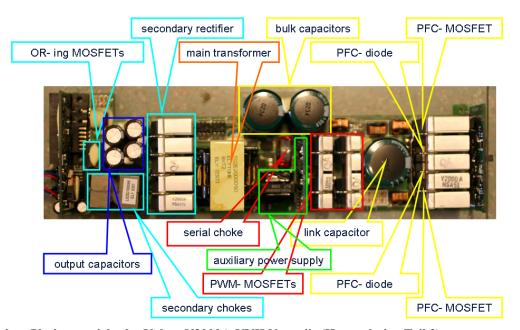

Die experimentellen Untersuchungen im Rahmen dieser Arbeit wurden im Jahr 2004 mit der Untersuchung von drei kommerziell erhältlichen Server-Schaltnetzteilen begonnen. Es wurden Netzteile der Hersteller Delta, Valere und Lite-On ausgewählt, die den Leistungsbereich von 500 W bis 2000 W abdecken (Abb. 2.4). Sie basieren alle auf dem im Markt dominierenden zweistufigen Konzept.

Abb. 2.4 Ansicht der untersuchten Server-SMPS

Schaltnetzteile mit einem dreistufigen Konzept waren zu diesem Zeitpunkt am Markt nicht verfügbar. Das zweistufige Konzept bedeutet, die Netzteile verfügen über eine PFC-Stufe mit nachfolgendem Hauptwandler. Die damalige Analyse, die wie folgt gegliedert ist, sollte die Grenzen der Topologien aufzeigen, die Designphilosophie des jeweiligen Herstellers offenlegen und Ansatzpunkte für Verbesserungen liefern.

#### Gliederung der Analyse:

- Schaltplanerstellung

- Topologieverständnis mit Hilfe von Simulationen

- Messungen elektrischer sowie thermischer Parameter

- Auswertung der gewonnen Daten

Die betrachteten Schaltnetzteile besitzen unterschiedliche Topologien und Schaltungsparameter, die in Tab. 2.1 gegenübergestellt sind. Im unteren Ausgangsleistungsbereich von 500 W bis 800 W dominieren Halbbrückenkonfigurationen als Hauptwandler, im höheren Leistungsbereich über 1000 W werden diese durch Vollbrückenanordnungen abgelöst.

| SMPS                | Delta                     | Lite-ON                      | Valere                     |

|---------------------|---------------------------|------------------------------|----------------------------|

|                     | DPS-500 EBA               | PS-3601-1F                   | V2000A-VVII                |

| Main-Topology       | Half bridge               | Asymmetric half bridge (TTF) | Full bridge                |

| PFC-Topology        | Boost-PFC                 | Boost-PFC                    | Interleaved Boost-PFC      |

| Input voltage range | 100 - 240 V               | 100 - 240 V                  | 200 - 240 V                |

| Output voltage      | 12 V <sub>DC</sub>        | $12 V_{DC}$                  | $48 V_{DC}$                |

| Output power        | 500 W                     | 600 W                        | 2000 W                     |

| PFC-frequency       | 100 kHz                   | 90 kHz                       | 70 kHz                     |

| Main-frequency      | 200 kHz                   | 110 kHz                      | 70 kHz                     |

| Power density       | 2,94 W/ inch <sup>3</sup> | 5,73 W/ inch <sup>3</sup>    | 17,65 W/ inch <sup>3</sup> |

| Cooling             | active cooled             | active cooled                | active cooled              |

Tab. 2.1 Parameter der untersuchten Server-SMPS

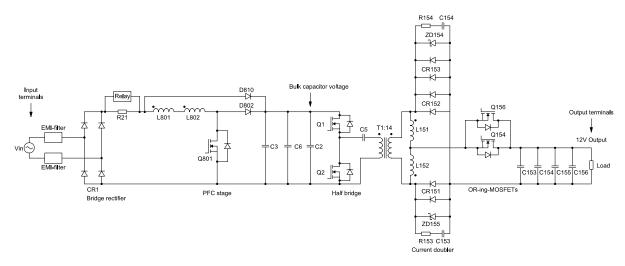

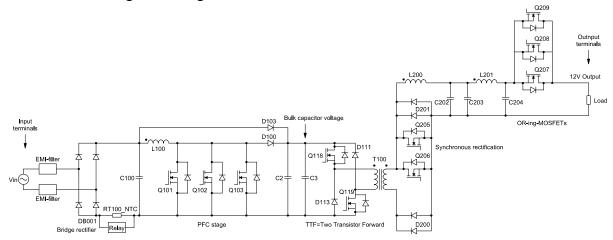

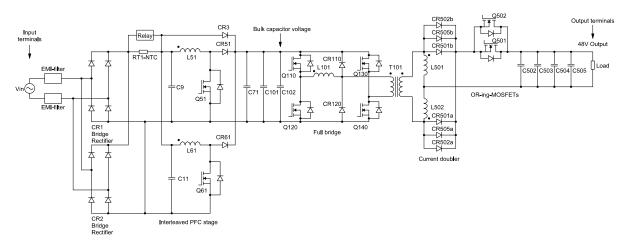

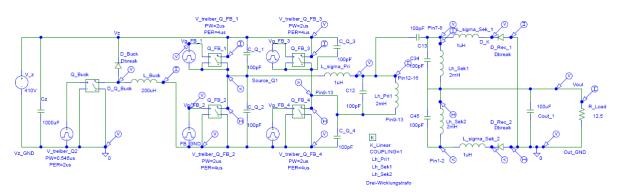

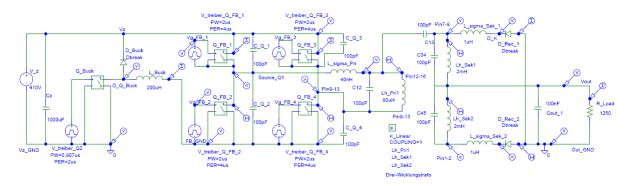

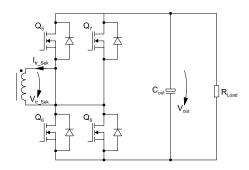

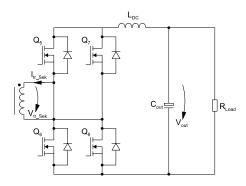

Die PFC-Stufen sind alle in der konventionellen Hochsetzsteller-Bauweise ausgeführt. Dabei existiert im SMPS des Herstellers Valere eine Besonderheit, da hier die PFC-Stufe durch zwei 180° phasenverschoben angesteuerte Hochsetzsteller gebildet wird. Diese Lösung wurde einer Parallelschaltung von PFC-MOSFETs vorgezogen. Diese Interleaved Boost-PFC-Stufe verkleinert die Stromwelligkeit für den Zwischenkreiskondensator sowie für das Eingangsfilter, was sich günstig auf die Dimensionierung und die Lebensdauer auswirkt. Weitere Vorteile sind in der besseren thermischen Balance zwischen den einzelnen Halbleitern bzw. den einzelnen Magnetbauelementen zu sehen. Ein Nachteil ist der höhere steuerungstechnische Aufwand. Detaillierte Betrachtungen zu PFC-Stufen werden im Kapitel 3.5 vorgenommen. Die Netzteile von den Firmen Delta und Lite-ON, deren Schaltpläne in Abb. 2.5 bzw. Abb. 2.6 zu sehen sind, können mit variabler einphasiger Wechselspannung im Bereich von 100 V \(\subseteq V\_{\text{IN RMS}} \le 240 V\) betrieben werden (Weitbereichseingang). Die Folge der Auslegung der PFC-Stufe auf Weitbereichseingang ist ein geringer Wirkungsgrad der PFC-Stufe im Vergleich zu einer PFC, die nur für einen schmalen Eingangsspannungsbereich dimensioniert wurde. Das betrachtete Schaltnetzteil der Firma Valere (Abb. 2.7) beispielsweise verfügt über einen kleinen Eingangsspannungsbereich. Die Schaltfrequenzen der verschiedenen PFC-Stufen sind sehr ähnlich. Sie liegen im Bereich von 70 kHz bis 100 kHz. Die Interleaved Hochsetzsteller-PFC erzeugt prinzipbedingt eine Frequenzverdopplung, die an Eingangsfilter und Zwischenkreiskondensator wirksam wird. Die höhere effektive Frequenz bewirkt infolge optimierter Auslegung eine Volumenreduktion der genannten Komponenten. In den Hauptwandler-Stufen wird mit sehr unterschiedlichen Frequenzen geschaltet, das Gerät der Firma Lite-ON arbeitet mit 110 kHz, das Netzteil der Firma Delta hingegen mit 200 kHz und das Gerät der Firma Valere beinhaltet eine Vollbrücke mit 70 kHz, bei der es topologiebedingt zu einer Frequenzverdopplung hinter dem sekundärseitigen Gleichrichter kommt.

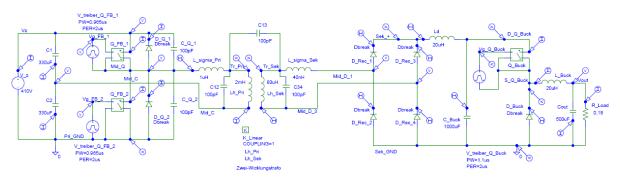

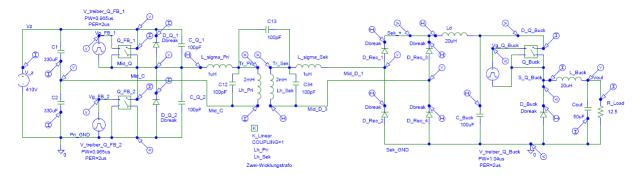

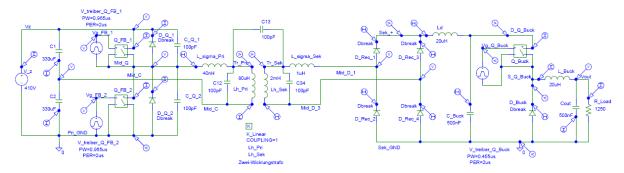

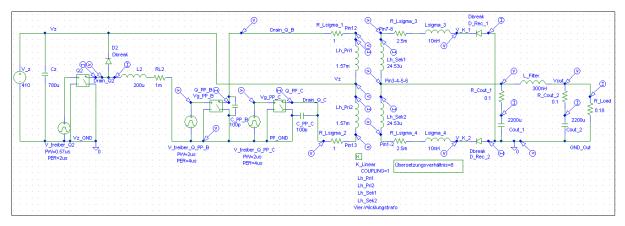

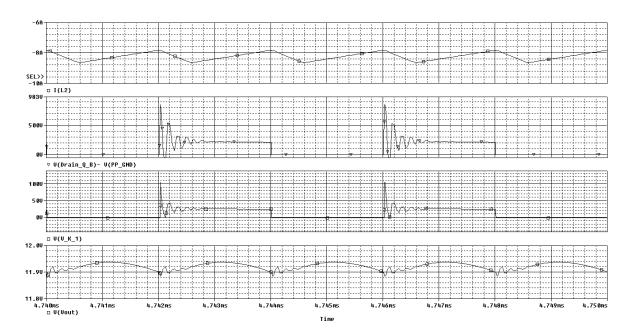

Abb. 2.5 Schaltplan des Delta DPS-500 EBA (Leistungsteil)

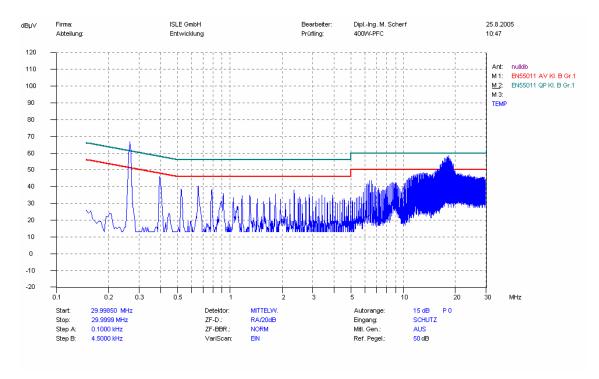

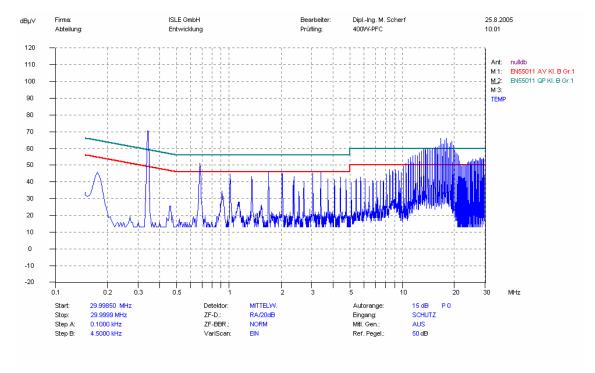

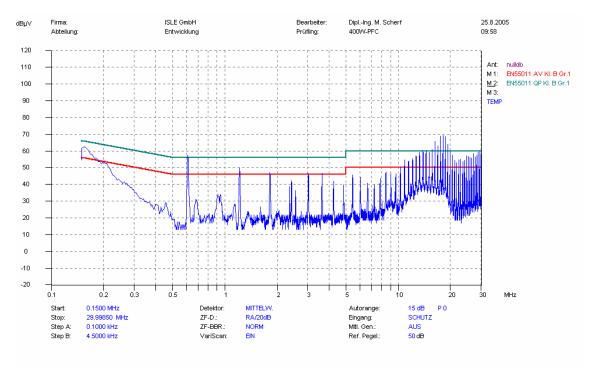

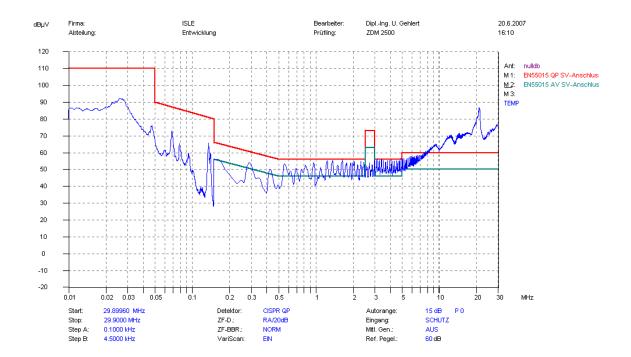

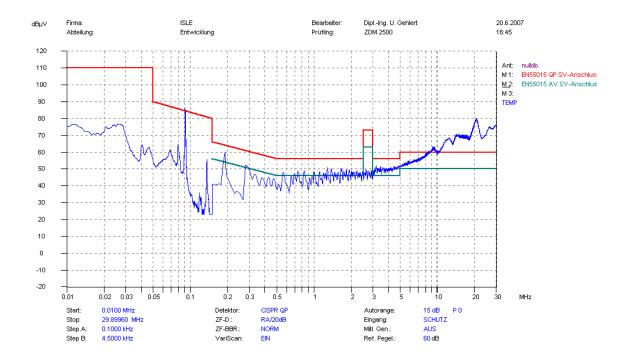

Es ist nachvollziehbar, dass die Schaltfrequenzen für die PFC-Stufe und den Hauptwandler unter dem Gesichtspunkt des günstigen EMV-Verhaltens ausgewählt wurden. Leitungsgebundene EMV wird im Frequenzbereich von 150 kHz bis 30 MHz gemessen, das bedeutet, dass alle Schaltfrequenzen im Gerät möglichst weit von dem Messstartpunkt 150 kHz entfernt sein sollten. Eine Entstörung des Gerätes mit einer Grundwelle nahe der Messstartfrequenz wäre sehr schwierig bis unmöglich.

Abb. 2.6 Schaltplan des Lite-ON PS-3601-1F (Leistungsteil)

Die im SMPS der Firma Delta verwendete Frequenz von 200 kHz stellt hinsichtlich der EMV kein Problem dar, da die EMV-Filterdämpfung im Bereich von 200 kHz sehr gut ist. Die EMV-Filterdämpfung nimmt mit steigender Frequenz zu. Die während der Analyse durchgeführten EMV-Messungen unterstreichen die theoretischen Annahmen und bestätigten die Einhaltung der EMV-Normen durch alle Geräte.

Die dem Anhang beigefügten Bilder Abb. A. 1 bis Abb. A. 6 zeigen die Platinen der verschiedenen Netzteile und geben einen Eindruck über die Größe der verschiedenen Komponenten unter dem Einfluss der Schaltfrequenz. Der Einfluss der Schaltfrequenz spiegelt sich bei den drei betrachteten SMPS nicht direkt in der Leistungsdichte wider. Die Leistungsdichte wurde über die Gehäuseaußenmaße und die Ausgangsleistung des Gerätes ermittelt. Die verschiedenen Kühlbedingungen infolge aktiver Kühlung, können in der Leistungsdichte-Betrachtung nicht berücksichtigt werden. Die Leistungsdichte ist also nur ein grober Vergleichswert für Netzteile und ist stark von der Designphilosophie abhängig.

Abb. 2.7 Schaltplan des Valere V2000A-VVII (Leistungsteil)

Das Netzteil der Firma Delta besitzt absolut gesehen die höchste Schaltfrequenz. Das Gesamtsystem weist aber die im Vergleich geringste Leistungsdichte von 2,94 W/inch³ auf. Das Gerät der Firma Valere besitzt hingegen die geringsten absoluten Schaltfrequenzen, verfügt aber aufgrund des gewählten Frequenzverdopplungskonzeptes und des guten thermischen Managements über die höchste Leistungsdichte im Vergleich (17,65 W/inch³).

Die Hauptwandler der drei SMPS sollen im Folgenden näher betrachtet werden.

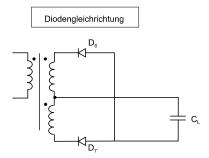

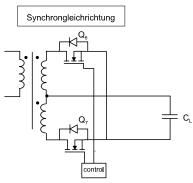

Das Gerät DPS-500 EBA des Herstellers Delta verfügt primärseitig über eine Halbbrücke mit Reihenkondensator, um die Flussbalance für den Transformator zu erreichen. Auf der Sekundärseite befindet sich ein DC-Mittelpunkt (current doubler) mit Diodengleichrichter. Diese Topologie kann theoretisch im Tastverhältnisbereich  $0 \le D \le 1$  arbeiten.

Das Gerät des Herstellers Lite-ON ist als Two Transistor Forward (TTF) ausgeführt. Der Gleichrichter ist hier teilweise mit MOSFETs im Synchronbetrieb realisiert. Die Schaltvorgänge der Topologie werden in [1.2] eingehend beschrieben. Der Arbeitsbereich dieser Topologie ist auf  $0 \le D \le 0.5$  begrenzt.

Die im Gerät V2000A-VVII vom Unternehmen Valere verwendete Vollbrücke kann im Tastverhältnisbereich  $0 \le D \le 1$  betrieben werden. Diese Topologie verfügt über ein patentiertes Ansteuerkonzept. Die high-side-MOSFETs arbeiten im Zero Voltage Switching (ZVS)-Betrieb, die low-side-MOSFETs der Vollbrücke schalten hart. Weiterhin verfügt diese Schaltung über eine Reiheninduktivität (L101) mit Clampingdioden (CR110, CR120) im Transformatorpfad. Diese Induktivität wirkt einerseits als Limitierung für den Stromanstieg (di/dt) in der Hauptstufe und andererseits als induktiver Spannungsteiler zwischen der internen Trafostreuung und der externen Reiheninduktivität. Diese beiden Wirkungen verringern die Überspannung an den sekundärseitigen Gleichrichterdioden, die mit einem DC-Mittelpunkt (current doubler) kombiniert sind. Zusätzlich unterstützt die Drossel den ZVS-Betrieb. Die Kombination von Ansteuerkonzept und Reiheninduktivität mit Clampingdioden führt zur Erzielung eines hohen Wirkungsgrades im Teillastbetrieb.

Alle untersuchten SMPS verfügen über OR-ing-MOSFETs, die das Netzteil im Fehlerfall vom Ausgang abtrennen können. Diese MOSFETs sind während des Normalbetriebs permanent eingeschaltet und sollten deshalb sehr niederohmig sein.

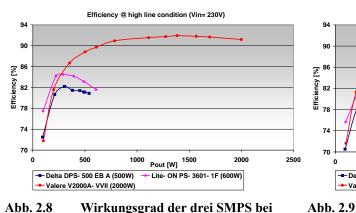

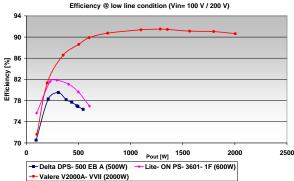

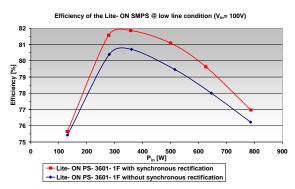

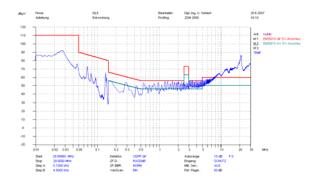

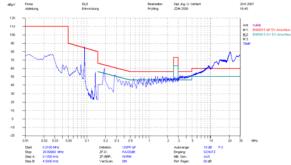

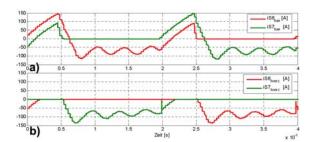

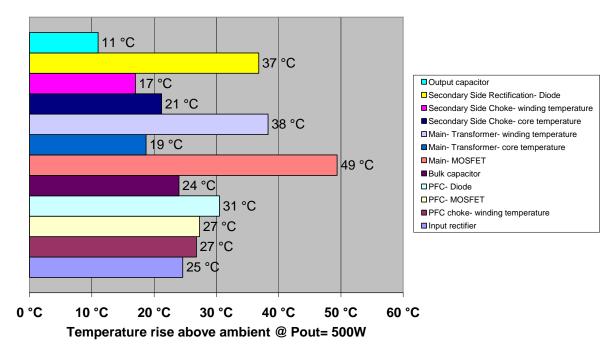

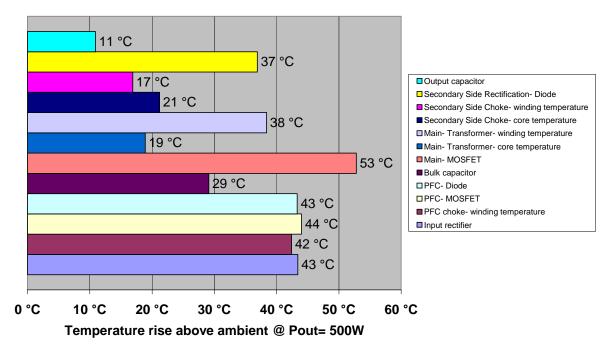

Die Wirkungsgrade der drei Schaltnetzteile sind in Abb. 2.8 für hohe Eingangsspannung und in Abb. 2.9 für niedrige Eingangsspannung dargestellt.

Das Gerät des Unternehmens Valere verfügt nur über einen kleinen Eingangsspannungsbereich von 200 V bis 240 V, wo hingegen die beiden anderen Geräte einen weiten Eingangsspannungsbereich von 100 V bis 240 V unterstützen. Ein kleiner Eingangsspannungsbereich wirkt sich positiv auf den Gesamtwirkungsgrad aus, da die PFC-Stufe für einen Arbeitspunkt optimiert werden kann.

Abb. 2.8 Wirkungsgrad der drei SMPS bei hoher Eingangsspannung  $V_{\rm IN~RMS}$ =230 V

Wirkungsgrad der drei SMPS bei niedriger Eingangsspannung V<sub>IN\_RMS</sub>=100 V für Delta & Lite-ON V<sub>IN\_RMS</sub>=200 V für Valere

Bei einer PFC für Weitbereichseingang wird diese für die minimale Eingangsspannung optimiert, beim Betrieb an hoher Eingangsspannung arbeitet sie dann meist nicht optimal.

Das Netzteil der Firma Valere besitzt im Vergleich den höchsten Wirkungsgrad (>90 %). Das resultiert aus mehreren Faktoren: Die relativ niedrige Schaltfrequenz bewirkt geringe Schaltverluste in den Halbleitern. Das gute thermische Management in Verbindung mit der Nutzung des Interleaved Boost-PFC-Konzeptes sorgt für eine optimale Verlustverteilung auf die einzelnen Bauelemente. Die hohe DC-Ausgangsspannung von 48 V bewirkt einen relativ niedrigen Strom im Vergleich zu einem 12 V System bei gleicher Leistung. Weiterhin positiv wirkt sich die Verwendung der Reiheninduktivität mit Clampingdioden auf die sekundärseitigen Überspannungen und somit auf die Gleichrichterdiodenauswahl aus.

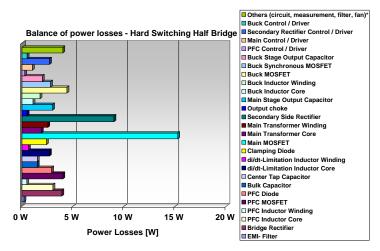

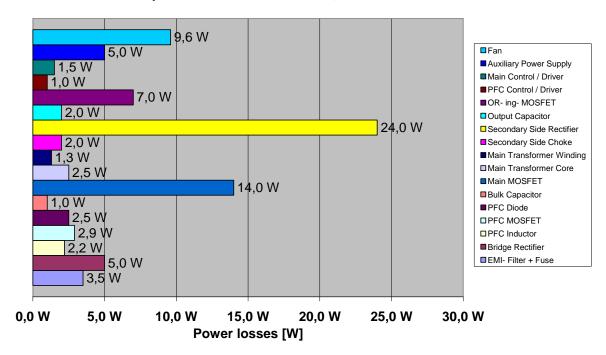

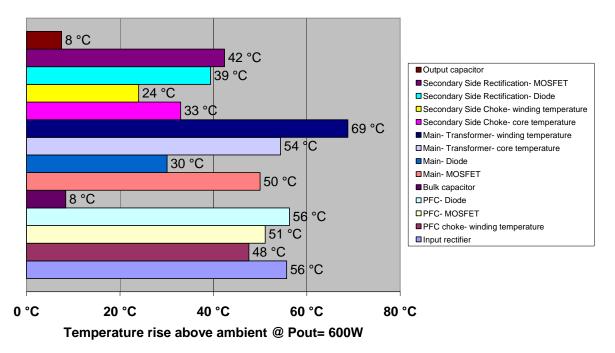

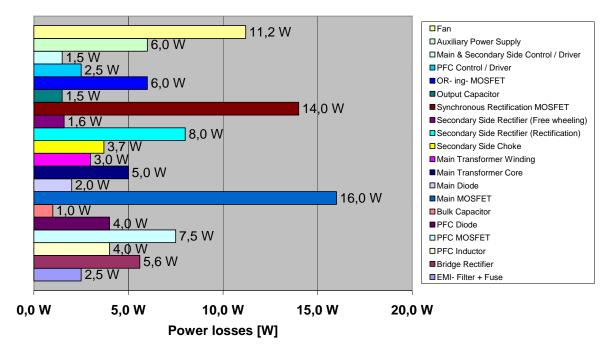

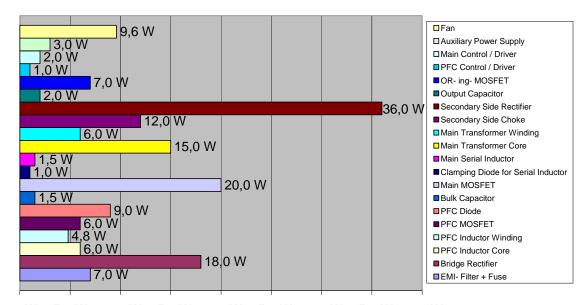

Das Schaltnetzteil der Firma Delta besitzt mit 81 % (V<sub>IN\_RMS</sub>=230 V/ P<sub>OUT</sub>=500 W) im Vergleich den niedrigsten Wirkungsgrad. Die Ursache liegt in der hohen Schaltfrequenz von 200 kHz in der Hauptstufe. Bestätigt wird diese Annahme durch die thermische Analyse im Anhang Abb. A. 7 und Abb. A. 8, wo eine hohe Temperatur der Hauptwandler-MOSFETs ersichtlich ist, die auf Schaltverluste zurückzuführen sind. Weitere wesentliche Verlustquellen sind die sekundärseitigen Gleichrichterdioden und die OR-ing-MOSFETs. Die Verlustverteilung auf die einzelnen Leistungskomponenten ist in Abb. A. 9 zu sehen. Der Transformator wurde auf eine geringe Übertemperatur optimiert, wie an dem Verhältnis von Kern- zu Wicklungsverlusten zu sehen ist. Betragen die Wicklungsverluste ca. die Hälfte der Kernverluste, so ist der Transformator auf ein Übertemperaturminimum optimiert [8.1].

Die Messungen am Gerät PS-3601-1F von Firma Lite-ON ergaben einen Gesamtwirkungsgrad von 82 % ( $V_{IN\_RMS}$ =230 V/  $P_{OUT}$ =600 W). Der Wirkungsgrad-Verlauf besitzt sein Maximum schon vor der maximalen Ausgangsleistung von 600 W. Das deutet auf eine optimierte Systemauslegung hin. Ein System, das seinen maximalen Wirkungsgrad bei größtmöglicher Ausgangsleistung besitzt, ist in den meisten Fällen überdimensioniert.

Die Hauptverluste entstehen beim Gerät von Firma Lite-ON in den Hauptwandler-MOSFETs und den sekundärseitigen Gleichrichtern (Abb. A. 12). Der sekundärseitige Gleichrichter ist teilweise mit MOSFETs bestückt, die im Synchronbetrieb operieren, was sich positiv auf den Gesamtwirkungsgrad auswirkt. Die Verluste des Transformators in diesem System sind relativ hoch, dies macht sich auch in der Übertemperaturbetrachtung Abb. A. 10 und Abb. A. 11 bemerkbar. Der Wirkungsgrad-Unterschied beim Betrieb mit hoher und mit niedriger Eingangsspannung ist bei allen Geräten sehr gut mittels der Übertemperaturbetrachtung zu erklären. In dem Eingangsfilter, dem Eingangsgleichrichter und den PFC-Komponenten entstehen durch den höheren Eingangsstrom höhere Verluste.

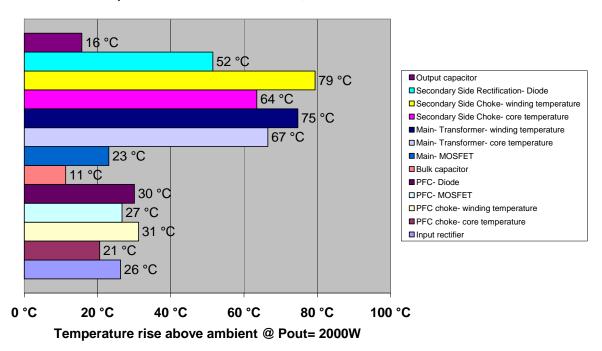

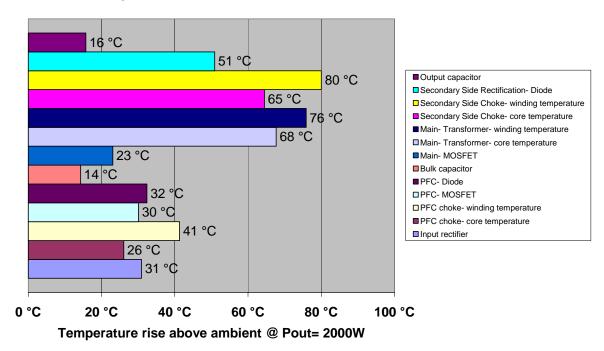

Die größten Verluste entstehen beim SMPS der Firma Valere in den sekundärseitigen Gleichrichterdioden, den MOSFETs der Vollbrücke und in dem Brückengleichrichter am Netzeingang (Abb. A. 15). Der Transformator ist, wie beim Netzteil von Firma Delta, auf ein Übertemperaturminimum optimiert. Der Gesamtwirkungsgrad wurde mit 91 % (V<sub>IN\_RMS</sub>=230 V/P<sub>OUT</sub>=2000 W) ermittelt. Bei der Betrachtung der Übertemperaturen ist kaum ein Unterschied zwischen 200 V und 230 V Eingangsspannung zu bemerken (Abb. A. 13, Abb. A. 14). Der Vergleich der verschiedenen Systeme lässt den Schluss zu, dass der Wirkungsgrad mit steigender Systemleistung größer wird, da ein System für höhere Ausgangsleistung gezielter als ein Netzteil für niedrige Ausgangsleistung optimiert werden kann. Die Ursache liegt darin, dass der Kostenaspekt mit steigender Ausgangsleistung etwas in den Hintergrund tritt. Der Energieaufwand zur Kühlung des SMPS ist bei allen untersuchten Netzteilen ein großer Anteil in der Verlustleistungsbilanz. Eine Systemoptimierung auf geringe Gesamtverluste wirkt sich auch positiv auf die Verkleinerung der Kühlleistung aus, was ein System nachhaltig verbessert.

Eine detaillierte Übersicht der experimentellen Untersuchungen zum Stand der Technik und eine Zusammenfassung zur Designphilosophie kann in Anhang Abb. A. 16 bis Abb. A. 20 nachgelesen werden.

Nachfolgend wird auf die Auswertung von Literaturquellen eingegangen, die sich mit dreistufigen Konzepten beschäftigen.

#### Ergebnisse der Literaturrecherche

Eine Literaturrecherche zum Beginn der Arbeit im Jahr 2004 lieferte keine Ergebnisse zur Thematik dreistufiger Schaltnetzteile. Eine spätere Recherche brachte zwei Veröffentlichungen aus dem Jahr 2006 hervor. Es wurde festgestellt, dass sich führende SMPS-Hersteller (Delta, Commergy, Emerson) mit der Thematik auseinandersetzen.

#### Mid-Power Breeze

Three stage topology

High low-line efficiency >89%, 90Vac/12V/33A

High power density > 20W/in3

Power: 200W – 1000W

Positioning: Global power, no derating

Efficiency Vs Load

92% 91% 90% 88% 88% 87% 86% 0 100 200 300 400 500

Abb. 2.10 Breeze Mid Power SMPS-Serie von der Firma Commergy; Eigenschaften der dreistufigen Topologien [7.10]

Abb. 2.11 Forced Resonant Bus Converter von der Firma Emerson Network Power; Hauptstufe der dreistufigen Topologie (LLC-Konverter) [Quelle: Firma Infineon]

Eine Veröffentlichung der Firma Commergy verweist auf die Breeze Mid Power SMPS-Serie, die ein dreistufiges Konzept besitzt und für einen hohen Wirkungsgrad bei niedriger Eingangsspannung (V<sub>IN\_RMS</sub>=90 V) konzipiert ist [7.10]. In Abb. 2.10 werden die Eckdaten der Topologie kurz zusammengefasst. Es wird auf einen hohen Teillastwirkungsgrad und eine

hohe Leistungsdichte >20 W/inch³ abgezielt. Die Leistungsdichte-Vergrößerung soll unter anderem mittels Einsparung von Zwischenkreiskapazität erreicht werden.

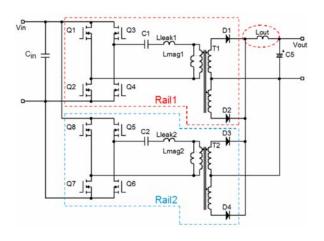

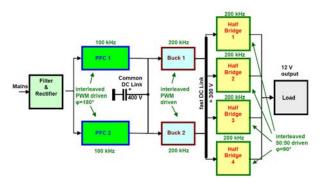

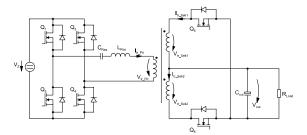

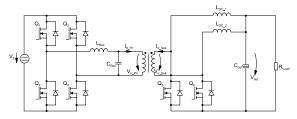

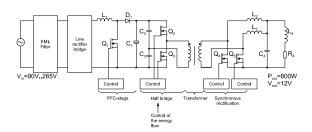

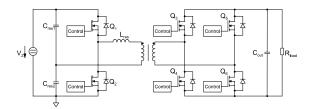

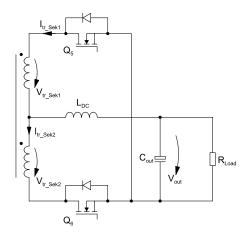

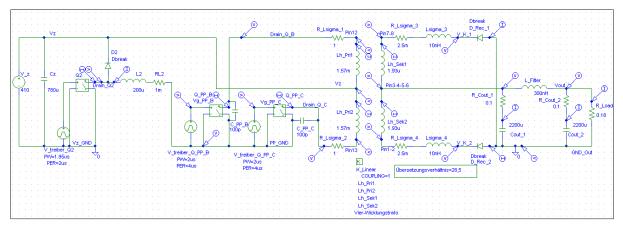

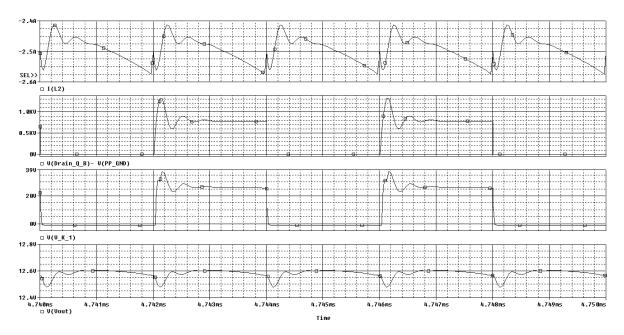

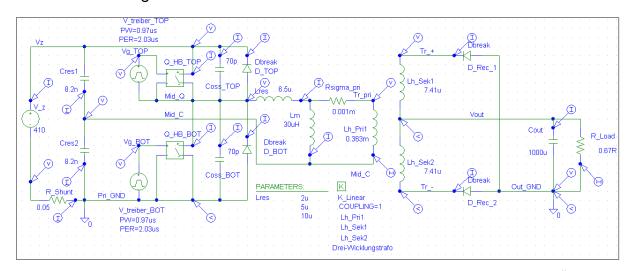

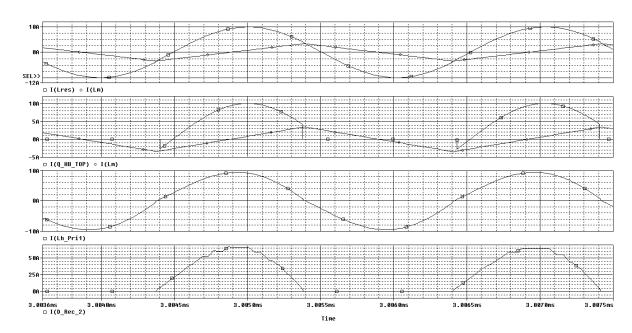

Das Unternehmen Emerson Network Power besitzt ebenfalls ein dreistufiges Schaltnetzteilkonzept in ihrem Lieferprogramm, den sogenannten Forced Resonant Bus Converter (Abb. 2.11). Dieser Konverter besteht aus einem primärseitig angeordneten Tiefsetzsteller zur Leistungsstellung und zwei versetzt getakteten LLC-Konvertern, die mit fester Frequenz und festem Tastverhältnis arbeiten. Das besondere an der Schaltung der LLC-Konverter ist, dass die Kommutierung zwischen den zwei Phasen durch die Ausgangsinduktivität (L<sub>OUT</sub>) erzwungen wird. Die Induktivität wirkt weiterhin positiv auf die Stromaufteilung zwischen beiden Zweigen und auf die Reduktion der Ausgangswelligkeit. Der Forced Resonant Bus Converter besitzt sehr hohe Teillastwirkungsgrade (>90 % bei 10 % Ausgangsleistung). Die vorgestellte Lösung wird im Ausgangsleistungsbereich von 200 W bis 3000 W eingesetzt.

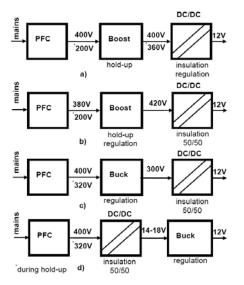

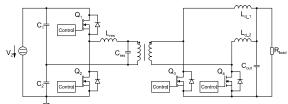

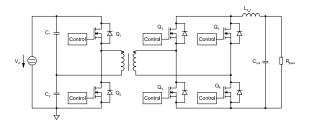

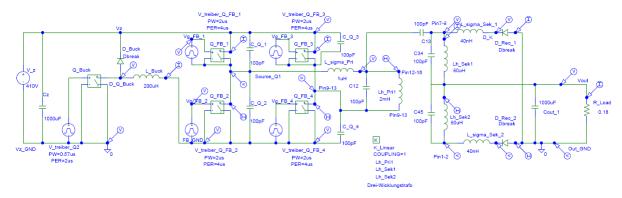

Die dritte interessante Veröffentlichung stammt von der Universität Paderborn in Zusammenarbeit mit dem Schaltnetzteilhersteller Delta Energy Systems [7.11]. In dieser Publikation werden die Vorteile von dreistufigen Konzepten erläutert und mehrere potentielle Ansätze auf theoretischer Basis gegenübergestellt (Abb. 2.12).

Abb. 2.12 Verschiedene Realisierungsmöglichkeiten für dreistufige Schaltnetzteile [7.11]

Abb. 2.13 Wirkungsgrad des dreistufigen 12 V/ 3 kW SMPS von der Firma Delta Energy Systems [7.11]

Abb. 2.14 Prinzipdarstellung des dreistufigen SMPS von der Firma Delta Energy Systems (3 kW/ 12 V) [7.11]

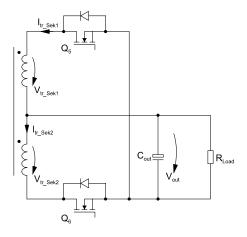

Aus dem Vergleich der primärseitig geregelten Schaltnetzteile (Pre-Regulated SMPS) und sekundärseitig geregelten Schaltnetzteile (Post-Regulated SMPS) kristallisierte sich für die Ausgangsleistung von 3 kW eine Lösung mit primärseitigem Tiefsetzsteller heraus (Abb. 2.12 c)). Die Lösung mit sekundärseitigem Tiefsetzsteller ist für 3 kW Ausgangsleistung, aufgrund des hohen Ausgangsstromes von 250 A in einem 12 V System, nicht praktikabel. Bei den Untersuchungen am DC-DC Konverter, der als reiner Gleichspannungstransformator ("DC-Transformator") arbeitet, wurden eine Halbbrücke, eine Vollbrücke und einen Interleaved Two Transistor Forward Konverter (ITTF) miteinander verglichen. Die Halbbrücke mit DC-Mittelpunkt (current doubler) wurde aufgrund der guten Transformatorausnutzung und der automatischen Transformatorflussbalance den anderen beiden Ansätzen vorgezogen. Die Veröffentlichung zeigt Ergebnisse eines 12 V/ 3 kW SMPS das mit zwei PFC-Stufen, zwei Tiefsetzstellern und vier Halbbrücken ausgestattet ist (Abb. 2.14). Die Tiefsetzsteller sind primärseitig angeordnet und übernehmen die Leistungsstellung und die Absicherung der Lastversorgung während Netzspannungsschwankungen (Erfüllung der hold-up time Anforderungen). Die Halbbrücken arbeiten mit einem konstanten Übertragungsverhalten. Je nach Leistungsbedarf können mehrere Halbbrücken ein- bzw. ausgeschaltet werden. Dieses Konzept erreicht über einen weiten Lastbereich einen hohen Wirkungsgrad von ca. 93 % (Abb. 2.13).

Die vorgestellten Veröffentlichungen lieferten für diese Arbeit wertvolle Hinweise bezüglich der Topologieauswahl. Sie unterstreichen nochmals die Aktualität dieser Arbeit.

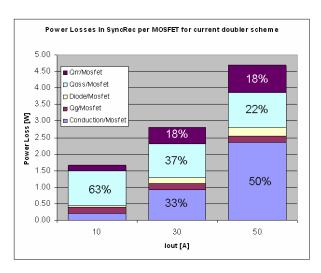

Die experimentelle Analyse zum Stand der Technik lieferte mehrere Ansatzpunkte für die Verbesserung von Schaltnetzteilen. Folgende Hauptverlustquellen sind zu optimieren: die Eingangsgleichrichter, besonders bei hoher Ausgangsleistung und niedriger Eingangsspannung; die primärseitigen Hauptwandler-MOSFETs; die OR-ing-MOSFETs und die sekundärseitigen Gleichrichter. Der Einsatz von Synchrongleichrichtern ist für die Erzeugung eines hohen Wirkungsgrades unerlässlich. Hohe Schaltfrequenzen bringen mit den verwendeten passiven und aktiven Bauelementen keinen Vorteil bezüglich des Wirkungsgrades. Topologien, die mit Frequenzverdopplung arbeiten, lieferten bessere Wirkungsgrade.

Während der Literaturrecherche wurden nur wenige Veröffentlichungen zur Thematik dreistufiger Schaltnetzteile gefunden, die aber hinsichtlich wichtiger Hinweise sehr ergiebig waren. Die gefundenen Literaturquellen unterstreichen die Wichtigkeit und Aktualität dieser Arbeit.

# 3. Analyse des Optimierungspotentials und Zielstellung der Arbeit

### 3.1 Vorbemerkungen

Nachdem der Stand der Technik auf dem Gebiet der Schaltnetzteile untersucht wurde, werden in diesem Kapitel die Optimierungspotentiale von Komponenten und Teiltopologien vorgestellt und Zielstellungen der Arbeit definiert. Die Auslotung der Potentiale erfolgt anhand von konkreten Muster- und Prinzipanalysen.

# 3.2 Leistungshalbleiter

#### 3.2.1 Vorbemerkungen

Die Kenntnis des elektrischen Verhaltens der Leistungshalbleiter ist für die optimale Auslegung eines Schaltnetzteils unabdingbar. Die experimentelle Analyse zum Stand der Technik hat gezeigt, wie groß der Anteil der Halbleiterverluste an den Gesamtverlusten eines SMPS ist. Es ist also notwendig, entsprechend der verfügbaren Halbleiter, die optimale Topologie auszuwählen, damit man ihre Vorteile bestmöglich ausnutzen kann.

Nach dieser kurzen Einführung beschäftigen sich die nachfolgenden Unterkapitel mit ausgewählten Schalterfamilien, die Verwendung im experimentellen Teil dieser Arbeit fanden.

#### 3.2.2 Hochvolt-Silizium (Si)-Leistungs-MOSFETs

Im Gegensatz zu Bipolar-Transistoren, bei denen – wie schon am Name ersichtlich – beide Ladungsträgerarten am Stromfluss beteiligt sind, tragen bei MOSFETs nur Majoritätsladungsträger zum Stromfluss bei: bei n-Kanal MOSFETs nur die Elektronen, bei p-Kanal Bauelementen nur die Löcher. Diese Eigenschaft hat zwei wesentliche Vorteile [2.7]:

- Der Drain-Source-Spannungsabfall eines Hochvolt-MOSFETs ist kleiner als dies bei der Sättigungskennlinie eines Bipolar-Transistors möglich ist. Insbesondere bei großen Strömen bedeutet das eine erhebliche Verlustreduktion.

- Da es sich bei einem MOSFET um ein unipolares Bauelement handelt, besitzt dieser im Durchlassfall keine Speicherladung. Der bei Bipolar-Bauelementen übliche Tailstrom bei Abschaltvorgängen ist deshalb nicht vorhanden. Extrem schnelle Schaltzeiten und deutlich geringere Schaltverluste machen den MOSFET deshalb zum idealen Schalter für getaktete Anwendungen wie Stromversorgungen.

In der Leistungselektronik werden fast ausschließlich selbstsperrende n-Kanal MOSFETs verwendet. Aus diesem Grund beschäftigt sich dieses und das folgende Kapitel 3.2.3 nur mit dieser Art Leistungs-MOSFETs. Leistungs-MOSFETs lassen sich in Abhängigkeit von ihrer Sperrspannungsklasse in Hochvolt- und Niedervolt-MOSFETs einteilen. Als Hochvolt-MOSFETs werden alle MOSFETs mit einer Sperrspannung  $V_{DS}>300~V$  bezeichnet. Für beide Typen gibt es unterschiedliche Anforderungen und Konzepte.

Grundlagen zu Aufbau und Funktionsweise von MOSFETs werden in [1.4] und [2.15] gegeben. Die Herausforderung des Hochvolt-Schalters liegt darin, dass er eine hohe Sperrfähigkeit mit sehr guten Eigenschaften im eingeschalteten Zustand verbinden soll. Weiterhin soll er einfach anzusteuern, schnell schaltbar, überlastfähig und natürlich billig sein. Für einen Halbleiter bedeutet die Anforderung - hohe Sperrspannung - eine niedrige Dotierung und eine relativ große Dicke der spannungsaufnehmenden Schicht. Aus dem Wunsch nach guten Durchlasseigenschaften resultieren dagegen eine hohe Dotierung und eine geringe Dicke der aktiven Schicht.

Dieser Widerspruch wurde als erstes mittels Hochvolt-Bipolar-Transistoren gelöst. Leider benötigen diese Schalter im eingeschalteten Zustand einen Basis-Strom, der nur um ein bis zwei Größenordungen unter dem Laststrom liegt, wodurch die Ansteuerschaltung sehr komplex wird. Hinzu kommen relativ hohe Parameterschwankungen [2.7].

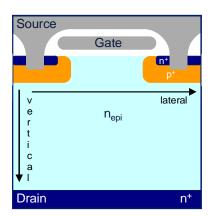

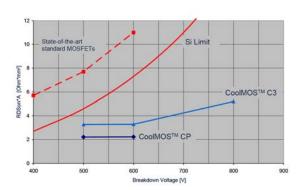

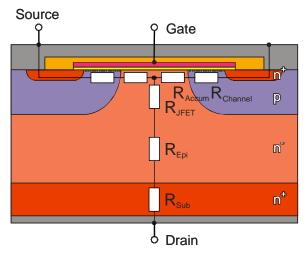

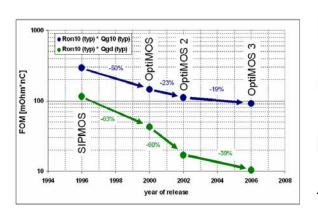

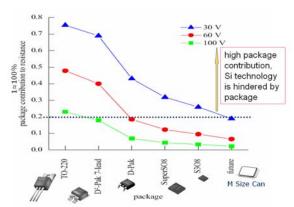

Bei den Schaltnetzteilen ist der MOSFET heute der dominierende Schalter. Der Elektronenstrom wird mithilfe eines lateralen oder vertikalen MOS-Kanal gesteuert und fließt bei Leistungstransistoren üblicherweise vertikal durch die spannungsaufnehmende Schicht zum rückseitigen Drain-Kontakt (Abb. 3.1). Um eine hohe Sperrfähigkeit zu erreichen, ist die Dotierung der spannungsaufnehmenden Schicht entsprechend niedrig. Da im eingeschalteten Zustand keine zusätzlichen Ladungsträger injiziert werden, zeigt dieses Konzept einen sehr hohen flächenspezifischen Widerstand, der als Funktion der Spannung überproportional stark mit einer Potenz zwischen 2,4 bis 2,6 ansteigt. Dieser gravierende Nachteil führt dazu, dass in der Anwendung versucht wird, mit einer möglichst geringen Sperrspannungsfähigkeit auszukommen, wie z.B. 450 V im amerikanischen Netz oder 500 V im 230 V Netz (PFC-Stufen). Als geeignetes Bewertungskriterium (Figure of merit) hat sich bei MOSFETs der sogenannte flächenspezifische Widerstand R<sub>DSon</sub>\*A etabliert. Er gibt an, welchen Einschaltwiderstand man mit einer Fläche von 1 mm² bei einer gegebenen Durchbruchsspannungsfestigkeit erzielen kann [2.7].

Die Weiterentwicklung des Konzepts in den 1980ern und 1990ern konnte diesen fundamentalen Nachteil bisher nicht lösen. Im günstigsten Fall erreicht man knapp das sogenannte Silizium-Limit, das sich als Lösung des zweidimensionalen Optimierungsproblems ergibt, wenn man mit einem Dotierungsverlauf Leitfähigkeit und Sperrfähigkeit gleichzeitig zu maximieren versucht [2.7]. Abb. 3.1 zeigt die Struktur eines konventionellen MOSFETs.

Abb. 3.1 Struktur eines konventionellen MOSFETs [Quelle: Firma Infineon]

Struktur eines MOSFETs mit Kompensationsprinzip, CoolMOS [Ouelle: Firma Infineon]

Wie aus der vorangegangenen Beschreibung ersichtlich stößt das Bauelementkonzepte an fundamentale physikalische Grenzen, die einer grundsätzlichen Optimierung des Hochvolt-Schalters in Richtung idealer Schalter im Wege stehen. Der hohe Einschaltwiderstand des MOSFETs - begrenzt durch das Silizium-Limit - ist das Haupthindernis für verlustleistungsarmen Stromfluss.

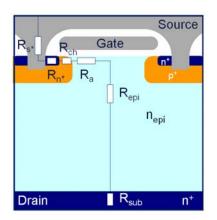

Abb. 3.2

Abb. 3.3 verdeutlicht, dass bei einem Hochvolt-Schalter der Hauptanteil am R<sub>DSon</sub> durch den Widerstand der Epitaxieschicht R<sub>epi</sub> gebildet wird. Von der Epitaxieschicht wird die Spannung aufgenommen. Die Dicke der Schicht bestimmt die Spannungsklasse des Bauelementes. Die Verbesserung des Hochvolt-Schalters ist folglich hier nicht evolutionär zu erreichen sondern nur mittels Adaption eines neuen Prinzips.

| VDS              | 30V | 600V  |

|------------------|-----|-------|

| R <sub>s</sub> . | 7%  | 0.5%  |

| R <sub>n</sub> + | 6%  | 0.5%  |

| R <sub>ch</sub>  | 28% | 1.5%  |

| Ra               | 23% | 0.5%  |

| R <sub>epi</sub> | 29% | 96.5% |

| R <sub>sub</sub> | 7%  | 0.5%  |

Abb. 3.3 Vergleich der Zusammensetzung des Durchlasswiderstandes bei Niedervolt- und Hochvolt-MOSFETs [Quelle: Firma Infineon]

Erinnert sei noch einmal an die Eingangsanforderungen an einen idealen Hochvolt-Schalter: hohe Sperrspannung, geringe Durchlassverluste, schnelles Schalten, Überlastfähigkeit, geringe Kosten. Man benötigt im eingeschalteten Zustand viele Ladungsträger, im Sperrfall dagegen wenige.

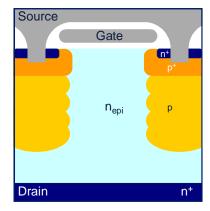

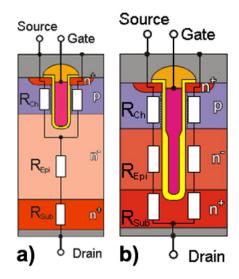

Die revolutionäre Lösung dieses Problems beruht darauf, beide Ladungsträgerarten im Bauelement räumlich voneinander zu trennen, sodass sich im Sperrfall ihre Nettoladung gegenseitig auf nahezu null ausgleicht. Im eingeschalteten Zustand dagegen steht die unverminderte Dotierung eines der beiden Ladungsträgertypen für den Stromfluss zur Verfügung.

Hiermit lässt sich auf einfache Weise das Silizium-Limit durchbrechen, da die Limitierung des konventionellen MOSFETs mit einem Dotierprofil Widerstand und Sperrspannung zu optimieren, nicht mehr existiert. Diese Idee hat aufgrund der ausgleichenden Wirkung der pund n-Gebiete zum Kompensationsprinzip geführt. Das Kompensationsprinzip ist seit langem für Lateraltransistoren als RESURF bekannt. Die Adaption auf Vertikaltransistoren galt jedoch lange Zeit als technologisch nicht machbar.

Die Anwendung in einem kommerziellen Produkt gelang erst 1998 mit dem als Markenzeichen eingetragenen CoolMOS-Transistor von Firma Infineon Technologies [2.7]. Zum heutigen Zeitpunkt gibt es bereits weitere Halbleiterhersteller die ein Kompensationsprinzip umgesetzt haben, dazu zählen unter anderen Fairchild, STMicroelectronics und Toshiba. Abb. 3.2 zeigt das Bauelementkonzept des CoolMOS.

Diese neuartige Struktur des CoolMOS-Transistors erlaubt eine drastische Reduktion des Einschaltwiderstands ( $R_{DSon}$ ), da nun das Dotierniveau der leitfähigen n-Zonen von der Sperrspannungsanforderung an das Bauelement entkoppelt ist. So benötigt man für ein höhersperrendes Bauelement zwar eine größere Dicke der spannungsaufnehmenden Zone und eine entsprechend tiefer reichende p-Säule, jedoch keine geringere Dotierung mehr. Damit wird der überproportional starke Anstieg des Einschaltwiderstands mit steigender Sperrspannung auf einen lediglich linearen Anstieg reduziert.

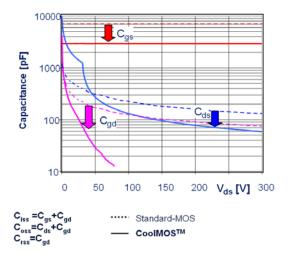

Abb. 3.9 zeigt die in der CoolMOS-Produktfamilie erzielten flächenspezifischen Widerstände als Funktion der Sperrspannung im Vergleich zu einer konventionellen Lösung und zum Silizium-Limit. Bei 600 V erreicht CoolMOS CP einen etwa Faktor fünf niedrigeren Widerstand, als die besten kommerziell erhältlichen konventionellen MOSFETs. Damit ist bei gegebener Fläche oder in einem gegebenen Transistorgehäuse ein entsprechend niedriger Einschaltwiderstand möglich (z.B. im TO-220 Gehäuse 99 m $\Omega$  statt 600 m $\Omega$  oder bei gegebenem Widerstand ein entsprechend kleinerer Chip bzw. ein entsprechend kleineres Package). Dieses Verkleinerungspotential ist insbesondere für Applikationen mit hoher Leistungsdichte von großem Vorteil.

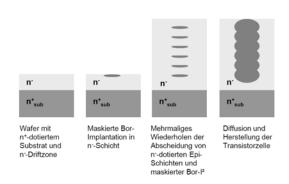

Abb. 3.4 Einzelschritte zum Aufbau der Säulenstruktur des Kompensationsbauelementes mittels Multiepitaxie-Verfahren [2.7]

Struktur eines Kompensationsbauelementes unter dem Rasterelektronenmikroskop (REM) [Quelle: Firma Infineon]

Die Herausforderung des CoolMOS-Konzepts liegt in der Herstellung der dicht gepackten, tief in die aktive Zone hineinreichenden p-Säulenstruktur und der exakten Kontrolle der Gesamtladung der jeweiligen p- und n-Säulen. Diese Ladungskontrolle hat erheblichen Einfluss auf die Sperrspannung des Bauelements und stellt heute eine prozesstechnisch gegebene Limitierung für Kompensationsbauelemente dar. Eine Weiterentwicklung der Bauelemente in Richtung noch niedrigerer Einschaltwiderstände erfordert daher begleitende Verbesserungen an den im Herstellungsprozess beteiligten Einzelprozessen. Als Herstellungsprozess hat sich heute bei allen kommerziell erhältlichen Produkten das Multiepitaxie-Verfahren durchgesetzt. Abb. 3.4 skizziert die Abfolge der benötigten Einzelprozessschritte [2.7]. Die im Ergebnis dieses Herstellungsprozesses entstehende Struktur wird im Abb. 3.5 als Rasterelektronenmikroskopieaufnahme dargestellt.

Abb. 3.5

Die Aufhebung des Zusammenhangs zwischen Durchbruchspannung und Durchlasswiderstand des klassischen MOSFETs ist die herausragende Eigenschaft des Kompensationsbauelements. Es wird durch die räumliche Trennung der p- und n-Gebiete innerhalb einer Transistorzelle erreicht. Die Einstellung der Dotierniveaus beider Gebiete erfolgt so, dass sich die Ladungen im Rahmen der Fertigungstoleranzen nahezu aufheben – sie kompensieren sich, daher der Name: Kompensationsbauelement.

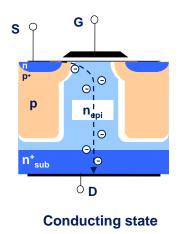

Nachfolgend wird eine kurze Zusammenfassung zur Funktion von Kompensationsbauelementen gegeben, die mittels Abb. 3.6 und Abb. 3.7 illustriert wird.

Abb. 3.6 Durchlassfall eines Kompensationsbauelementes [2.7]

Sperrfall eines Kompensationsbauelementes [2.7]

Abb. 3.7

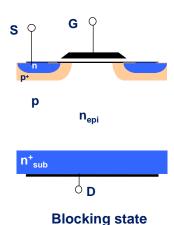

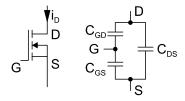

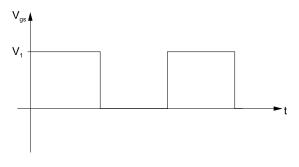

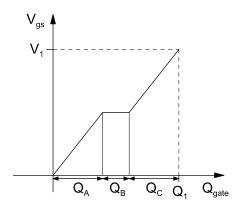

Bei Anlegen einer Spannung im Sperrbetrieb werden die Ladungsträger zunächst entlang der Umfanglinie des pn-Übergangs der beiden Dotiergebiete ausgeräumt. Es entsteht eine Raumladungszone längs der Säulenstruktur, die primär eine laterale Feldkomponente erzeugt. Die Ladungsträger werden dabei in der p- und n-Säule quasi von zwei Seiten aus der Driftstrecke herausgepresst. Bereits bei relativ geringen Spannungen (typisch <50 V) ist die Säulenstruktur vollständig ausgeräumt und die Raumladungszone wirkt wie eine quasi intrinsische Schicht. Sobald die gesamte Säulenstruktur ausgeräumt ist, erfolgt die weitere Sperrspannungsaufnahme über ein Ansteigen des vertikalen elektrischen Feldes in der Raumladungszone und über eine vertikale Ausdehnung der Raumladungszone in der verbleibenden Driftstrecke. Es bildet sich eine Feldverteilung, bei der sich laterale und vertikale Feldkomponente überlagern. Für eine maximale Durchbruchspannung bei gleichzeitig bestmöglichem Durchlassverhalten sind vertikale und laterale Feldkomponente idealerweise gleich groß [2.7]. Der beschriebene Aufbau der Raumladungszone über die Säulenstruktur der p- und n-Gebiete bei Anlegen einer Sperrspannung macht sich über den Sperrfall hinaus auch beim Ein- und Ausschalten bemerkbar. Da die p- und n-Gebiete bereits bei relativ geringer Sperrspannung, sprich am Anfang des Schaltvorgangs, vollständig ausgeräumt werden, ist die Raumladungszone bereits nach sehr kurzer Zeit aufgebaut. Dies führt zu einem stark nichtlinearen Verlauf der Drain-Source-Kapazität C<sub>DS</sub> oder Ausgangskapazität C<sub>OSS</sub>, da sich im Gegensatz zum klassischen MOSFET nicht nur die Weite der Raumladungszone mit steigender Spannung ändert sondern darüber hinaus auch die Oberfläche der mit jeweils Source und Drain verbundenen p- und n-Gebiete. Sobald die p- und n-Säulen bei etwa 50 V ausgeräumt sind, erreicht die Ausgangskapazität infolge der kleineren Chip-Fläche einen sehr niedrigen, nun nahezu spannungsunabhängigen Wert. Die Gate-Drain-Kapazität C<sub>GD</sub> oder Rückwirkungskapazität besitzt aufgrund der raschen Ausdehnung der Raumladungszone in der n-Säule ebenfalls einen stark nichtlinearen Verlauf mit sehr kleinen Werten über 50 V. Die Gate-Source-Kapazität profitiert in erster Linie vom Flächenshrink, der durch das Kompensationsprinzip im Vergleich zu konventionellen Power-MOSFETs ermöglicht wird. Abb. 3.8 zeigt eine Gegenüberstellung der Transistorkapazitäten eines konventionellen MOSFETs mit einem CoolMOS für jeweils 600 V sperrende Bauelemente mit 190 mΩ Einschaltwiderstand. Es fällt die starke Nichtlinearität der Kapazitäten C<sub>DS</sub> und C<sub>GD</sub> auf, die sich im Schaltverhalten der MOSFETs widerspiegelt.

Abb. 3.8 Bauteilkapazität des CoolMOS im Vergleich zu Standard-Transistoren (Vergleichsbasis: 600 V/ 190 m $\Omega$ ) [2.7]

Abb. 3.9 R<sub>DSon</sub>\*A des CoolMOS als Funktion der Durchbruchsspannung im Vergleich zu einem Standard MOSFET und zum Silizium-Limit [2,1]

Neben den Kapazitäten spielt natürlich auch die Schaltgeschwindigkeit und die sich hieraus ergebende zeitliche Überlappung von Strom und Spannung eine Rolle. Beim Ausschalten wird der Elektronenstrom über den MOS-Kanal abgeschnürt. Die beweglichen Ladungsträger der p- und n-Säule fließen dabei als Majoritätsträgerdriftstrom zu ihren jeweiligen Kontaktgebieten der mit Source verbundenen p-Wanne und dem mit Drain verbundenen rückseitigen n<sup>+</sup>-Substrat. Die Ladungsträger überqueren dabei nicht die sich aufspannende Raumladungszone. Mit anderen Worten: Es entstehen kaum Jouleschen Verluste im Bauelement.

Die Schaltgeschwindigkeit hängt daher im Wesentlichen von der Umladung der Gate-Elektrode und damit von der Gate-Source-Kapazität, der Gate-Drain-Kapazität und der Leistung der Gate-Treiberstufe ab. Typische Schaltzeiten liegen im Nanosekundenbereich.

Beim Einschalten muss die Raumladungszone durch die Neutralisierung der geladenen Akzeptoren und Donatoren in der p- und n-Säule wieder abgebaut werden. Die Elektronen werden dabei vom Kanalstrom gestellt, die Löcher fließen hingegen als Driftstrom aus der p-Wanne in die p-Säule hinab.

Eine hohe Schaltgeschwindigkeit erfordert daher eine niederohmige Verbindung und somit im Herstellungsprozess eine entsprechend gute Justage und Verbindung der einzelnen p-Implantationsinseln. Typische Schaltzeiten liegen ebenfalls im Bereich weniger Nanosekunden. Damit zählen Kompensationsbauelemente wie der CoolMOS zu den schnellsten am Markt verfügbaren Hochvolt-Schaltern [2.7].

Eine Konsequenz des Flächenshrinks der CoolMOS-Technologie ist, dass die Stromflussdichte im Bauelement höher ist als in konventionellen Transistoren. Damit werden die Anforderungen an die Robustheit z.B. die Beherrschung des Kurzschlussfalles entsprechend verschärft. Der Kurzschlussstromverlauf des Standard-MOSFETs ist durch eine ungenügende Stromsättigung gekennzeichnet, d.h. der Kurzschlussstrom nimmt mit steigender Drain-Source-Spannung zu und erreicht bereits bei applikationstypischen Spannungen von etwa 400 V den siebenfachen Nennstrom.

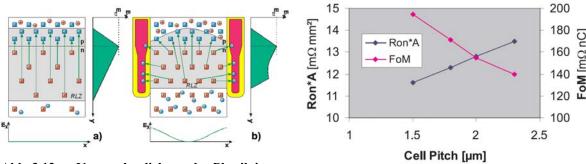

Konventionelle Power MOSFETs verfügen daher nicht über die gewünschte Eigenschaft, den Kurzschlussstrom auf niedrige Werte zu begrenzen, was für einen sicheren Betrieb im Grenzbereich notwendig ist. Das Kompensationsbauelement zeigt hier trotz sehr hoher Stromdichten ein deutlich besseres Verhalten. Grund hierfür ist die Säulenstruktur der p-Gebiete, die einen mit ansteigender Spannung immer weiter abschnürenden vertikalen Junction Gate Field Effect Transistor (JFET) darstellt. Der Kurzschlussstrom wird so sehr wirkungsvoll begrenzt und weist einen nahezu konstanten Wert über der gesamten Safe Operating Area (SOA) auf. Gibt es für das Kompensationsprinzip eine physikalische Grenze? Mittels Verkleinerung des Abstandes der p- und n-Gebiete und der gleichzeitigen Erhöhung der Dotierung in diesen lässt sich bei konstanter Durchbruchspannung theoretisch der Durchlasswiderstand immer weiter verringern. In der Realität begrenzen jedoch einerseits die Lithographie und die Prozesskontrolle der p- und n-Dotierung den maximal erreichbaren R<sub>DSon</sub>-Gewinn. Andererseits wird bei sehr kleinen Strukturbreiten, durch den oben beschriebenen JFET, die Leitfähigkeit im Durchlassfall bereits bei sehr geringen anliegenden Spannungen beschränkt.

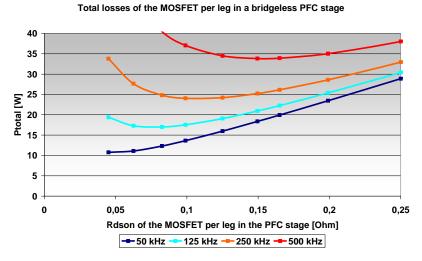

Bei der Auswahl eines Schalters für eine Applikation ist es wichtig, einen Kompromiss zwischen Schaltverlusten, Durchlassverlusten und Ansteuerverlusten zu finden. Grundsätzlich besitzen MOSFETs mit einem geringen Durchlasswiderstand, bedingt durch die große Chip-Fläche, auch große Kapazitäten. Besonders bei hohen Schaltfrequenzen (>100 kHz) sind also Schaltverlusten und Ansteuerverlusten besondere Bedeutung beizumessen.

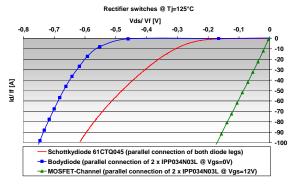

Die Body-Dioden der heutigen Hochvolt-MOSFETs sind noch nicht so gut, dass sie periodisch kommutiert werden könnten. Deshalb gibt es in der praktischen Anwendung auch keine Applikation, die diesen Betrieb nutzt. Verluste durch die Speicherladung der Body-Diode sind bei Hochvolt-MOSFETs deshalb nicht zu berücksichtigen.

Bei Hochvolt-MOSFETs kann man grundsätzlich sagen, dass die Einschaltverluste gegenüber den Ausschaltverlusten dominieren. Dieses Verhalten ist durch die Ausgangskapazität C<sub>OSS</sub> des MOSFETs in Kombination mit den parasitären Kapazitäten in der Schaltung (z.B. Trafokapazität) zu begründen. Diese Kapazitäten müssen bei einem Einschaltvorgang entladen werden und es würden Verluste entstehen. Bei einem Ausschaltvorgang hingegen wirken diese Kapazitäten entlastend und reduzieren damit die Ausschaltverluste. Der vom MOSFET getragene Strom wird beim Ausschaltvorgang von der Ausgangkapazität C<sub>OSS</sub> übernommen und verursacht im MOS-Kanal keine Verluste mehr.

Weiterführende Informationen zu Kompensationsbauelementen bezüglich des Schaltverhaltens, Technologiegrenzen, Avalanche (Lawinendurchbruch)-Charakteristik und Trends werden in der Literatur [2.3], [2.7], [2.1] gegeben.

Die Applikation von Kompensationsbauelementen stellt neue Anforderungen an die Schaltungsentwicklung und das Schaltungslayout, um die hohen Schaltgeschwindigkeiten zu beherrschen. Folgende Applikationshinweise sind zu beachten:

- Die Schaltgeschwindigkeit des MOSFETs kann durch den Gate-Vorwiderstand R<sub>G</sub> beeinflusst werden.

- Die Entkopplung des Treiber-Source-Anschlusses vom Leistungs-Source-Anschluss ist nötig (durch eine Source-Gegenkopplung kann es zu Schwingungen in den Stromund Spannungsverläufen kommen).

- Eine geringe Koppelkapazität zwischen Drain und Gate ist nötig, um Schwingungen in der Gate-Spannung so gering wie möglich zu halten.

- Die Verwendung eines symmetrischen Layouts ist für die Parallelschaltung von MOS-FETs nötig.

- Ein mehrlagiges PCB-Layout begünstigt schnelle, störungsfreie Schaltvorgänge.

- Die Anordnung des Gate-Treibers nahe am MOSFET ist nur bei extremen Schaltvorgängen nötig. Diese treten in der Praxis kaum auf. Im Normalfall überdämpft der Widerstand R<sub>G</sub> die aufgrund von L und C verursachte Schwingung in der Gate-Zuleitung.

Dieser Abschnitt hat einen Überblick über den aktuellen Entwicklungsstand bei Hochvolt-MOSFETs gegeben. Im Rahmen dieser Arbeit wurde auf Produkte der Firma Infineon zurückgegriffen, da diese Produkte im Ergebnis vergleichender Untersuchungen den höchsten Entwicklungsstand aufwiesen. Ein Großteil der Bauelemente stand bereits als Vorserienmuster (Samples) für Untersuchungen zur Verfügung.

Bei Hochvolt-Schaltern wird der Durchlasswiderstand  $R_{DSon}$  nahezu komplett durch den Epitaxiewiderstand  $R_{epi}$  gebildet. Das folgende Kapitel beschäftigt sich mit Niedervolt-MOSFETs. Bei diesen Bauelementen wird der  $R_{DSon}$  hingegen aus mehreren Anteilen gebildet. Dominierend sind hier der Kanalwiderstand  $R_{ch}$ , der Akkumulationswiderstand  $R_a$  und der Epitaxiewiderstand  $R_{epi}$  (Abb. 3.3).

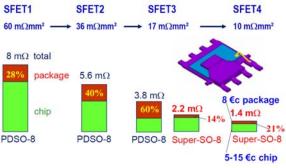

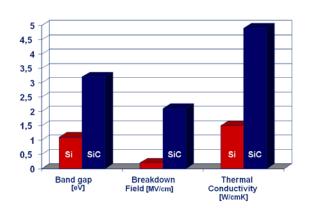

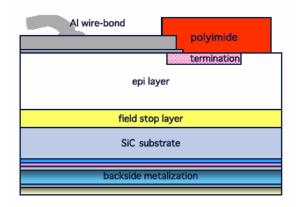

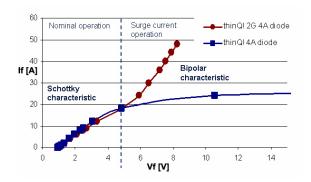

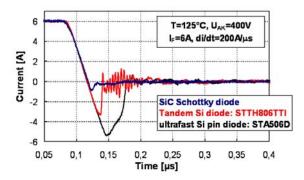

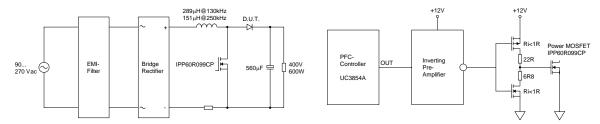

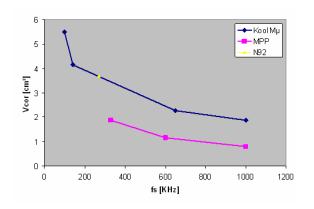

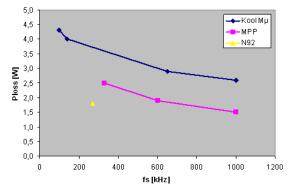

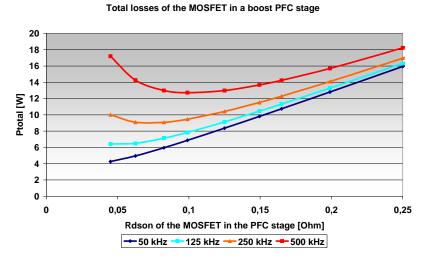

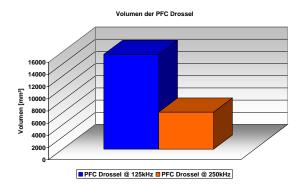

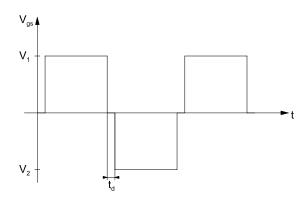

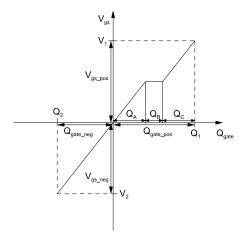

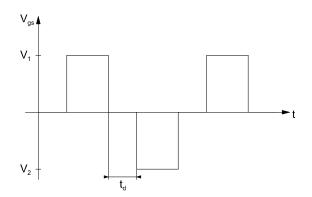

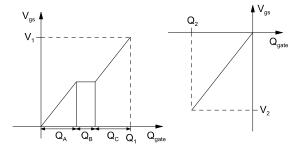

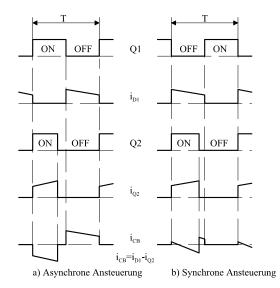

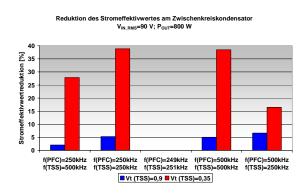

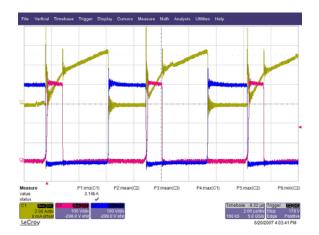

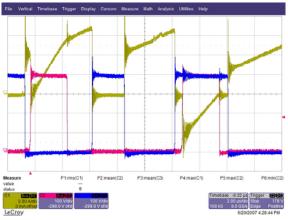

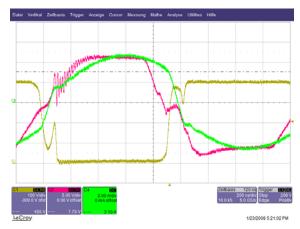

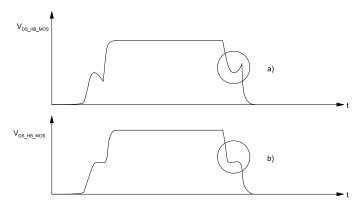

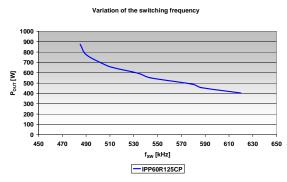

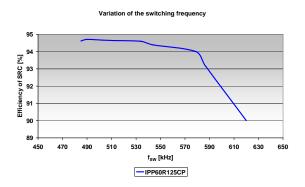

# 3.2.3 Niedervolt-Silizium (Si)-Leistungs-MOSFETs