### **51. IWK**

**PROCEEDINGS**

11-15 September 2006

# FACULTY OF ELECTRICAL ENGINEERING AND INFORMATION SCIENCE

INFORMATION TECHNOLOGY AND ELECTRICAL ENGINEERING - DEVICES AND SYSTEMS, MATERIALS AND TECHNOLOGIES FOR THE FUTURE

Startseite / Index:

http://www.db-thueringen.de/servlets/DocumentServlet?id=12391

### **Impressum**

Herausgeber: Der Rektor der Technischen Universität Ilmenau

Univ.-Prof. Dr. rer. nat. habil. Peter Scharff

Redaktion: Referat Marketing und Studentische

Angelegenheiten Andrea Schneider

Fakultät für Elektrotechnik und Informationstechnik

Susanne Jakob

Dipl.-Ing. Helge Drumm

Redaktionsschluss: 07. Juli 2006

Technische Realisierung (CD-Rom-Ausgabe):

Institut für Medientechnik an der TU Ilmenau

Dipl.-Ing. Christian Weigel Dipl.-Ing. Marco Albrecht Dipl.-Ing. Helge Drumm

Technische Realisierung (Online-Ausgabe):

Universitätsbibliothek Ilmenau

ilmedia

Postfach 10 05 65 98684 Ilmenau

Verlag:

Verlag ISLE, Betriebsstätte des ISLE e.V.

Werner-von-Siemens-Str. 16

98693 Ilrnenau

© Technische Universität Ilmenau (Thür.) 2006

Diese Publikationen und alle in ihr enthaltenen Beiträge und Abbildungen sind urheberrechtlich geschützt. Mit Ausnahme der gesetzlich zugelassenen Fälle ist eine Verwertung ohne Einwilligung der Redaktion strafbar.

ISBN (Druckausgabe): 3-938843-15-2 ISBN (CD-Rom-Ausgabe): 3-938843-16-0

Startseite / Index:

http://www.db-thueringen.de/servlets/DocumentServlet?id=12391

U. Schwalbe T. Reimann

## Einsatz von SiC-Bauelementen in der elektronischen Stromversorgungstechnik

### **Power electronics**

### Kurzfassung

Silizium-Karbid-Leistungshalbleiter (SiC) werden im nächsten Jahrzehnt einige Bereiche der Leistungselektronik revolutionieren. Im Moment muss die Kostensituation von SiC-Bauelementen verbessert werden, um das Marktpotential zu vergrößern.

Dieser Beitrag beschäftigt sich mit der Rolle von Silizium-Karbid-Halbleitern in Hochleistungsschaltnetzteilen, bei denen höchste Wirkungsgrade erzielt werden sollen. Die Betrachtungen beziehen sich auf typische Applikationen im Server- und Telekom-Stromversorgungsbereich, da in diesen Sparten die Ausgangsleistung bei konstanten Kosten und gleich bleibender Größe pro Jahr um 20% steigen muss. Diese Anforderungen stellen immer höhere Ansprüche an den Wirkungsgrad der Schaltnetzteile, die mit Hilfe von SiC-Bauelementen erreicht werden können.

Der Fokus dieses Artikels wird auf den Stand der Technik bei ausgewählten aktiven SiC-Bauelementen und deren Applikation gelegt. Als Applikationsbeispiele für SiC-SBD (SiC-Schottky-Barriere-Diode) werden PFC-Stufen und Hochvolt-Tiefsetzsteller angeführt. Zur Anwendung von aktiven SiC-Bauelementen wird ein hartschaltender Tiefsetzsteller mit SiC-VJFETs (Vertikale JFETs) und SiC-SBD bei 200kHz Schaltfrequenz vorgestellt.

Weiterführende Untersuchungen beschäftigen sich mit dem Systemvorteil durch 600V SiC-Bauelemente gegenüber Si-Bauelementen in Höchstfrequenz-PFC-Stufen bis 1MHz Schaltfrequenz.

### 1 Silizium-Karbid-Bauelemente Stand der Technik und Ausblicke

### 1.1 SiC-Schalter

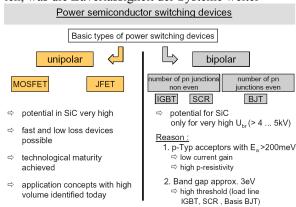

Der Fokus bei der Entwicklung von SiC-Bauelementen ist heute auf aktive Schalter gerichtet. Dabei stehen mehrere Konzepte zur Auswahl (siehe **Bild 1**), die im Folgenden näher erläutert werden.

### 1.1.1 Bipolare SiC-Schalter

Als Vertreter der Gruppe "Bipolare Bauelemente" sind der BIFET (Bipolar-Injection-FET) und der IGBT zu nennen. Beim BIFET handelt es sich um eine bipolare "Normally-on-JFET"-Struktur, mit der Sperrspannungen von bis zu 4,5kV angestrebt werden. Die Kombination eines SiC-BIFET mit einem

Niedervolt-Si-MOSFET in einer Kaskodenschaltung schafft ein "Normally-off"-Bauelement, dessen Dynamik mithilfe des Si-MOSFET kontrolliert werden kann /4/. Der BIFET kann bei Hochspannungsanwendungen, insbesondere in der Medizintechnik, einen Ersatz für die Reihenschaltung von Si-IGBTs darstellen, was die Zuverlässigkeit der Systeme weiter

**Bild 1** Typen von Leistungshalbleitern /3/

erhöhen wird. Für Sperrspannungen kleiner als 4kV sind unipolare SiC-Schalter eine weitere Möglichkeit zur Herstellung vorteilhafter Bauelemente aus SiC.

### 1.1.2 Unipolare SiC-Schalter

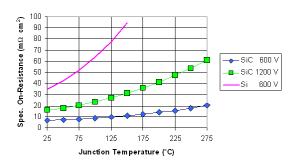

In der Gruppe der unipolaren Schalter gibt es zwei grundlegende Schalterkonzepte, die den Sperrspannungsbereich von 600V bis ca. 2kV abdecken können. Die aktuellen Untersuchungen bewegen sich sowohl um den SiC-MOSFET, der ein "Normally-Off" Verhalten aufweist, als auch um den SiC-JFET, der eine "Normally-On" Charakteristik besitzt. Die Kombination eines SiC-JFET mit einem Niedervolt Si-MOSFET in einer Kaskodenschaltung schafft wiederum ein "Normally-off"-Bauelement, dessen Dynamik mit Hilfe des Si-MOSFET kontrolliert werden kann. Unipolare SiC-Bauelemente bieten nicht nur ein herausragendes dynamisches Verhalten, sondern auch Vorteile bezüglich des statischen Verhaltens. Die sehr geringen spezifischen Durchlasswiderstände (R<sub>DSon</sub>) werden beim MOSFET durch die sehr kurzen Kanäle und die hohe Kanaldichte erreicht. Diese Maßnahmen kompensieren die minderwertige Charakteristik in SiC. Beim JFET wird der geringe spezifische Durchlasswiderstand durch einen sehr großen Kanal realisiert. Der spezifische Einschaltwiderstand (spez. R<sub>DSon</sub>) eines großflächigen 600V JFETs von SiCED bei Raumtemperatur liegt um das 5-fache niedriger als der entsprechende Wert eines 600V CoolMOS-Kompensationsbauelementes (siehe Bild 2). Bei Betriebstemperatur der Bauelemente wird dieser Unterschied weiter vergrößert, wodurch der Vorteil von SiC-Bauelementen noch deutlicher wird.

Bild 2 Erhöhung des spezifischen Einschaltwiderstandes mit zunehmender Temperatur bei einem SiC-VJFET im Vergleich zum Si-CoolMOS/1/

Der beschriebene Vorteil wird in einer Applikation aber nicht direkt zum Einsatz kommen, da ein SiC-JFET für eine gegebene Strombelastung eine geringere aktive Fläche aufweist als ein Si-CoolMOS. Die Vorteile des geringen spezifischen Einschaltwiderstandes und der damit verbundenen kleinen Bauelementefläche beim JFET bringen eine dynamische Verbesserung des Bauelementes durch geringere Ein-

gangs- und Ausgangskapazitäten gegenüber einem Si-CoolMOS. Der thermische Widerstand (R<sub>th</sub>) eines SiC-JFET ist größer als der eines Si-MOSFETs gleicher Stromklasse. Die Bauelementekapazitäten eines 1200V SiC-JFET verhalten sich im Vergleich zu einem 800V Si-CoolMOS wie in **Gleichung 1** dargestellt. Mit einem SiC-Device hat man weiterhin die Möglichkeit, in Hochtemperatur-Applikationen vorzudringen, bei denen Sperrschichttemperaturen von mehr als 200°C vorhanden sind. Diese Tendenz ist bereits in **Bild 2** zu erkennen. Die hohen Temperaturen bringen neben Vorteilen auch neue Herausforderungen an das Packaging des Bauelementes mit sich.

$$C_{DS\_JFET\_1200\ V} = 0.1 \cdot C_{DS\_CoolMOS\_800\ V}$$

$C_{GD\_JFET\_1200\ V} = 0.1 \cdot C_{GD\_CoolMOS\_800\ V}$

$C_{GS\_JFET\_1200\ V} = 0.05 \cdot C_{GS\_CoolMOS\_800\ V}$

Gleichung 1 Kapazitätsvergleich SiC-JFET zu Si-CoolMOS

### 1.1.2.1 **SiC-MOSFET**

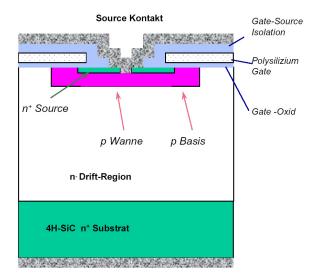

Der SiCED SiC-MOSFET ist ein "Normally-off"-Bauelement, das über ein isoliertes Gate gesteuert wird. Dieses Device besitzt eine einfache planare Struktur (siehe **Bild 3**) und kann mit Gatespannungen  $(V_{GS})$  von bis zu 20V betrieben werden.

Drain Kontakt

Bild 3 Struktur eines SiCED SiC-MOSFET /3/

Beim aktuellen Entwicklungsstand des SiCED SiC-MOSFETS existieren noch einige Problemstellungen, die weiterentwickelt werden müssen. Dazu gehören das ESD-empfindliche Gate und die geringe Ladungsträgermobilität im Kanal des SiC-MOSFETs. Bei einem 1000V Si-MOSFET trägt die Driftzone im Ge-

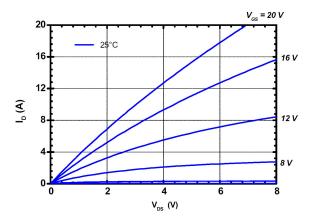

gensatz zum Kanal einen viel größeren Anteil zum R<sub>DSon</sub> bei. Beim aktuellen Entwicklungsstand des SiC-MOSFETs ist dieses Verhältnis jedoch noch umgekehrt. Das heißt, der Kanal liefert einen Hauptanteil zum R<sub>DSon</sub>. Im weiteren Entwicklungsverlauf muss der Kanalwiderstand weiter verringert werden. Möglichkeiten dazu bieten spezielle Oxidtechniken, die Verwendung ultra kurzer Kanäle oder veränderte Kristallorientierungsrichtungen, welche weniger Interface-Defekte als thermisch gewachsene SiO<sub>2</sub>-Schichten aufweisen. Offene Fragen gibt es auch bezüglich der Oxid-Zuverlässigkeit und dem Betrieb unter hohen Temperaturen /3/. **Bild 4** zeigt das Ausgangskennlinienfeld eines SiCED 1200V/ 10A SiC-MOSFETs in der Entwicklungsphase.

**Bild 4** Ausgangskennlinienfeld eines SiCED 1200V/ 10A SiC-MOSFET (Entwicklungsmuster) /3/

An der Kennlinie ist die starke Abhängigkeit des  $R_{DSon}$  von der Gatespannung ( $V_{GS}$ ) zu sehen. **Tabelle** 1 hingegen verdeutlicht die geringe Temperaturabhängigkeit des  $R_{DSon}$  beim SiC-MOSFET.

| $T_{j}$ | <b>V</b> <sub>GS</sub> | R <sub>on</sub> | specific R <sub>on</sub> |

|---------|------------------------|-----------------|--------------------------|

| 25°C    | 20 V                   | 0.27 Ω          | 12 mΩcm²                 |

| 125°C   | 20 V                   | 0.31 Ω          | 14 mΩcm <sup>2</sup>     |

Tabelle 1 Durchlasswiderstand eines SiCED 1200V/ 10A SiC-MOSFET (Entwicklungsmuster) /3/

Der SiCED SiC-MOSFET ist in der aktuellen Entwicklungsphase noch nicht applizierbar, bietet aber aufgrund der genannten positiven Eigenschaften ein Potential für neue Anwendungsfelder speziell im Hochtemperatur-, Hochspannungs- oder auch Hochfrequenzbereich (Medizintechnik, Automotive usw.).

### 1.1.2.2 SiC-JFET

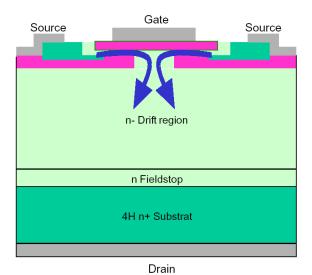

Der SiCED SiC-JFET ist im Gegensatz zum SiC-MOSFET ein "Normally-on"-Device, welches über einen pn-Übergang gesteuert wird (siehe **Bild 5**). Auf-

grund der "Normally-on"-Charakteristik benötigt man beim Betrieb des SiC-JFET ein anderes Treiberkonzept als bei einem konventionellen "Normally-off" Bauelement. Der JFET wird mit einer Gatespannung kleiner 0V ausgeschaltet. Bei einem Wert von 0V hingegen befindet er sich im leitenden Zustand. Dieses Verhalten wird in den meisten spannungsgespeisten Topologien als negativ angesehen, da es im Fehlerfall zum Zweigkurzschluss kommen kann. In einer stromgespeisten Topologie hingegen ist das "Normallyon"-Verhalten als positiver Aspekt zu werten. Vorteile des bereits gut entwickelten SiCED SiC-JFET sind die geringen Durchlasswiderstandswerte (R<sub>DSon</sub>), das Vorhandensein einer robusten Gatestruktur und die integrierte Bodydiode, welche in der Applikation genutzt werden kann. Die interne Funktion des JFET basiert nur auf einem pn-Übergang, der auch noch bei

Bild 5 Struktur eines SiCED SiC-VJFET /3/

sehr hohen Temperaturen von mehreren 100°C arbeitet. Somit gibt es beim JFET kein Problem mit der Zuverlässigkeit eines Gateoxids, wie es beispielsweise bei einem MOSFET der Fall ist. Die Schwellenspannung des JFET ist im Gegensatz zum MOSFET praktisch unabhängig von der Temperatur, weil die "Pinch-off"-Spannung im JFET nur durch die Kanalgeometrie und die Kanaldotierung bestimmt ist. Als weiterer wichtiger Punkt ist anzumerken, dass auch das "Reverse Recovery" des JFET nahezu temperaturunabhängig ist und somit auf ein Derating bei steigender Betriebstemperatur verzichtet werden kann, da keine zusätzlichen dynamischen Verluste entstehen. Die exzellente Kurzschlussfestigkeit des JFET ist ein Aspekt, der bei den Betrachtungen des Bauelementes nicht zu vernachlässigen ist. Sie liegt deutlich über der eines Si-CoolMOS. Der SiC-JFET bietet natürlich auch die Möglichkeit für eine Applikation im Hochtemperaturbereich /1/.

Nach einer grundlegenden Einführung in den aktuellen Stand der SiC-Schalterentwicklung folgt nun die

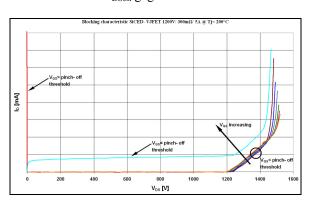

konkrete Betrachtung eines 1200V/ 5A SiCED VJFET, der bei einer Sperrschichttemperatur (T<sub>i</sub>) von 25°C einen Durchlasswiderstand (R<sub>DSon</sub>) von 300mΩ aufweist. Die grundlegenden Eigenschaften des Bauelementes wurden in statischen Messungen untersucht. Die dabei gewonnenen Erkenntnisse werden im Folgenden näher erläutert. Bild 6 zeigt die "Forward blocking characteristic", an der das Verhalten des VJFET in Abhängigkeit von der Gatespannung (V<sub>GS</sub>) zu sehen ist. Da das Device ein "Normally-on"-Verhalten aufweist, ist bei V<sub>GS</sub>=0V der Kanal für den Stromfluss geöffnet, und mit zunehmender negativer Spannung V<sub>GS</sub> wird beim Erreichen der Abschnürspannung ("Pinch-off"-Spannung) der Kanal des Bauelementes geschlossen. Ein Stromfluss (ID) ist somit nicht mehr möglich. Der JFET kann jetzt Sperrspannung aufnehmen; im Beispiel beträgt diese 1200V. Für positive Gatespannungen V<sub>GS</sub> wird die SiC-pn-Diode, die sich zwischen Gate und Source befindet, ab einer Schwelle leitend. Man spricht in diesem Betriebsfall vom Bipolar-Modus des JFET, da ständig ein Strom IG ins Gate des Devices fließt. Der Bipolar-Modus führt nicht zu einer Verringerung des Durchlasswiderstandes R<sub>DSon</sub> gegenüber seinem Wert bei

**Bild 6** "Forward blocking characteristic" eines SiCED VJFET 1200V/  $300m\Omega$ / 5A bei  $T_j$ =200°C

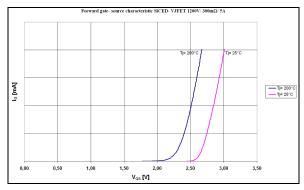

$V_{GS}$ =0V, da die Stromverstärkung des SiCED JFET dafür zu gering ist. Das Verhalten des JFET bei  $V_{GS}$ >0 wird mit der "Forward Gate-Source characteristic"

Bild 7 ,,Forward Gate-Source characteristic" eines SiCED VJFET 1200V/300mΩ/5A

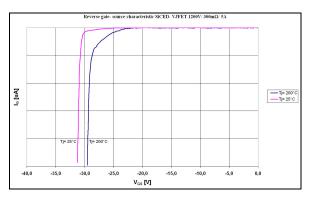

(siehe **Bild 7**) beschrieben, die einen negativen Temperaturkoeffizienten aufweist. Die Schleusenspannung  $V_{GS}$  der Gate-Source-Diode verändert sich von 2,5V auf 2V bei einer Temperaturerhöhung von 25°C auf 200°C. Das Verhalten der SiC-pn-Diode zwischen Gate und Source bei Anlegen einer negativen Gatespannung  $V_{GS}$  wird mit der "Reverse Gate-Source characteristic" beschrieben (siehe **Bild 8**). Die Gate-Source-pn-Diode geht bei  $V_{GS}$ =-31V in den

Durchbruch, sodass ein Strom aus dem Gate des JFET fließt. Die "Reverse Gate-Source characteristic" besitzt einen positiven Temperaturkoeffizienten, sodass es zu einer Zunahme der Durchbruchsspannung von 31V auf -29,5V kommt, wenn die Sperrschichttemperatur auf 200°C erhöht wird. Das Temperaturverhalten der "Reverse Gate-Source characteristic" des JFET ist für den Betrieb des SiCED VJFET nicht von Vorteil. Mit steigender Temperatur wird der bereits kleine Abstand zwischen "Pinch-off"-Spannung, bei welcher der Kanal abgeschnürt wird, und der Schwelle, bei der es zum Durchbruch der Gate-Source-Diode kommt, weiter verkleinert. Dieses Verhalten muss bei der Treiberapplikation beachtet werden.

**Bild 8** "Reverse Gate-Source characteristic" eines SiCED VJFET  $1200V/300m\Omega/5A$

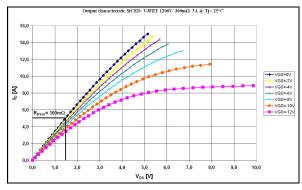

Die "Output characteristic" (siehe **Bild 9/ Bild 10**) gibt Aufschluss über das Durchlassverhalten des Si-CED VJFET in Abhängigkeit von der Gatespannung  $V_{GS}$ . Es ist zu sehen, dass der JFET mit  $V_{GS}$ =0V durchgesteuert ist und bei 25°C einen  $R_{DSon}$  von

**Bild 9** "Output characteristic" eines SiCED VJFET  $1200V/300m\Omega/5A$  bei  $T_i=25$ °C

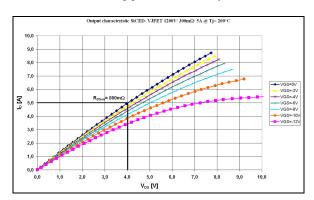

300m $\Omega$  aufweist. Bei Erhöhung der Sperrschichttemperatur auf 200°C kommt es zu einer Vergrößerung des  $R_{DSon}$  um den Faktor 2,7 auf ca. 800m $\Omega$ . Messungen der "Output characteristie" für  $V_{GS}$ >0V haben gezeigt, dass es im Bipolar-Modus zu keiner merklichen Verkleinerung des Durchlasswiderstandes  $R_{DSon}$  kommt. Somit kann bei der Ansteuerung des SiCED VJFET auf die Bereitstellung einer positiven Gatespannung verzichtet werden. Der Treiber muss lediglich zwischen  $V_{GS}$ =0V und der negativen "Pinchoff"-Spannung schalten. Neben der "Output Characteristic", die das Vorwärtsverhalten des JFET darstellt, gibt es noch die "Reverse output characteristic" (siehe Bild 11/ Bild 12). Diese beschreibt den JFET-Kanal in Rückwärtsrichtung parallel zur Bodydiode.

**Bild 10** "Output characteristic" eines SiCED VJFET  $1200V/300m\Omega/5A$  bei  $T_i=200^{\circ}C$

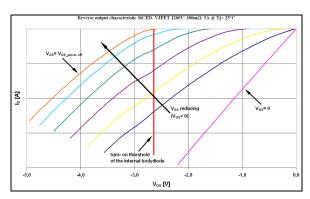

Der JFET-Kanal wird auch mit  $V_{GS}$ =0V in Rückwärtsrichtung aufgesteuert. Er weist in dieser Richtung ebenfalls eine ideale  $R_{DSon}$ -Gerade auf, die bei 25°C einen Wert von 300m $\Omega$  besitzt. Bei einer Sperrschichttemperatur von 200°C erhöht sich der  $R_{Dson}$  um einen Faktor von ca. 2,3 auf 680m $\Omega$ .

**Bild 11** "Reverse output characteristic" eines SiCED VJFET  $1200V/300m\Omega/5A$  bei  $T_i$ =25°C

Die Abschnürung des Kanals in Rückwärtsrichtung erfolgt bei Erreichen der negativen "Pinch-off"-Spannung  $V_{GS}=V_{GS\_pinch-off}$ . An diesem Punkt wird die ideale  $R_{DSon}$ -Gerade verlassen und nur die Bodydiode des JFET ist weiterhin für die Stromführung vorhanden. Die Abschnürspannung in Rückwärtsrichtung

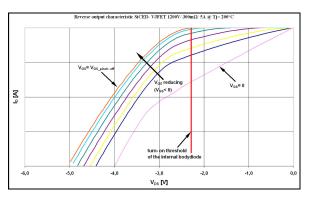

besitzt einen betragsmäßig größeren Wert als die in Vorwärtsrichtung. Die "Reverse output characteristic" (siehe **Bild 11**), bei der  $V_{GS}=V_{GS\_pinch-off}$  erreicht, besitzt bei  $V_{DS}=-2,7V$  einen Knick. Dieser charakterisiert die Schleusenspannung der SiCED JFET Bodydiode. Der Wert der Schleusenspannung  $V_{DS}=-2,7V$  ist in allen Kurvenverläufen als Bogen zu erkennen. Dieser beschreibt die Einschaltschwelle der JFET-Bodydiode, ab der es zu einer Stromaufteilung zwischen Kanal und Diode kommt. Bei einer

**Bild 12** "Reverse output characteristic" eines SiCED VJFET  $1200V/300m\Omega/5A$  bei  $T_i=200^{\circ}C$

Sperrschichttemperatur von 200°C sinkt der Betrag der Schleusenspannung der Bodydiode auf  $V_{DS}$ =-2,3V. An diesem Verhalten ist der negative Temperaturkoeffizient der Vorwärtsspannung (- $V_{DS}$ ) zu erkennen.

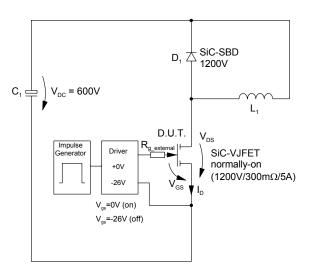

**Bild 13** Tiefsetzsteller zur dynamischen Messung an einem SiC-VJFET

Die gezeigten statischen Messergebnisse beschreiben den SiCED VJFET 1200V/ 300m $\Omega$ / 5A in allen Kennlinienbereichen. Für den Übergang zur praktischen Anwendung des Devices sind dynamische Messungen, die im Folgenden durch einige ausgewählte Arbeitspunkte des SiCED VJFET 1200V/ 300m $\Omega$ / 5A dokumentiert sind, unerlässlich. Die dafür verwendete

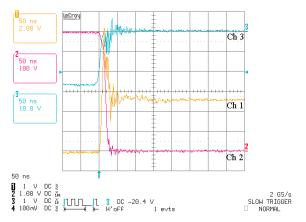

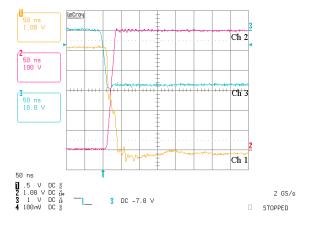

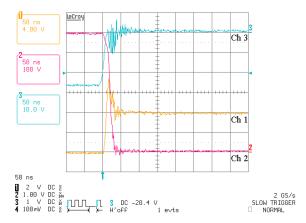

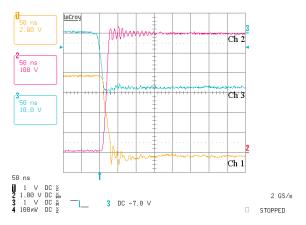

Tiefsetzstelleranordnung ist in **Bild 13** zu sehen. Die Oszillogramme für den Einschaltvorgang (siehe **Bild 14**/ **Bild 16**) bzw. die Graphen für den Ausschaltvorgang (siehe **Bild 15**/ **Bild 17**) sind unter den nachfolgenden Messbedingungen entstanden: Zwischenkreisspannung  $V_{DC}$ =600V, Gatevorwiderstand Rg=15Ω und Sperrschichttemperatur  $T_i$ =200°C.

**Bild 14** Einschaltvorgang eines SiCED VJFET 1200V/  $300 \text{m}\Omega$ / 5A bei  $T_j$ =200°C/  $I_D$ =5A/  $V_{DC}$ =600V Ch1:  $I_D$  Ch2:  $V_{DS}$  Ch3:  $V_{GS}$

Der verwendete niederinduktive Messaufbau besitzt eine Induktivität von ca. 45nH. Die Einschaltverläufe zeigen sowohl für einen Strom von  $I_D$ =5A, als auch für einen Strom  $I_D$ =8A keine besonderen Auffälligkeiten.

Die Spitzen im Stromverlauf  $I_D$  sind kapazitiver Natur und werden durch die Kapazitäten der SiC-Diode und der Lastdrossel verursacht. Ebenso wie die Einschaltvorgänge kommen auch die Ausschaltvorgänge für die beiden Ströme einem idealen Schaltvorgang sehr nah. Abschaltüberspannungen  $V_{\rm DS}$  sind nicht vorhanden. Es wurde in keinem der Verläufe Schwingungsverhalten festgestellt.

Bild 16 Einschaltvorgang eines SiCED VJFET 1200V/ 300m $\Omega$ / 5A bei  $T_j$ =200°C/  $I_D$ =8A/  $V_{DC}$ =600V Ch1:  $I_D$  Ch2:  $V_{DS}$  Ch3:  $V_{GS}$

Nachdem in Kapitel 1 das Verhalten von SiC-Bauelementen beschrieben wurde, werden im folgenden Abschnitt mögliche Applikation näher erläutert.

### 2 Applikation von Silizium-Karbid-Bauelementen in Schaltnetzteiltopologien

Frühe Visionen, wonach Si-Power-Bauelemente vollständig durch SiC-Bauelemente ersetzt werden sollten, haben sich bislang nicht erfüllt. Denn auch auf dem Sektor der Siliziumbauelemente hat es Weiterentwicklungen gegeben, die deren Präsenz in verschiedenen Applikationen weiterhin rechtfertigen; so z.B. der ladungsträgerkompensierte CoolMOS MOS-FET der Infineon Technologies AG. Die Einsatzfelder von SiC-Bauelementen liegen vielmehr in der Erschließung neuer Applikationen. Wenn man die Betrachtungsweise vom Bauelementelevel auf das Systemlevel erweitert, werden die Vorteile von SiC-Devices schnell ersichtlich. Beispielsweise können

bei der Verwendung höherer Schaltfrequenzen passive Komponenten verkleinert werden, was eine Gesamtsystemkostenreduktion hervorruft. Des Weiteren können Systeme beim Einsatz von SiC-Devices mit höheren Spannungsniveaus arbeiten, was bisher nicht nutzbare Topologien neu aufleben lässt. Ein Beispiel hierfür ist die Applikation von Single-Transistor-Topologien anstelle von Halb- oder Vollbrücken im Leistungsbereich bis 1kW. Die Realisierung von Hochtemperaturanwendungen ist bei Entwicklung geeigneter Packaging-Technologien auch vorstellbar.

# 2.1 Vergleich von Si-CoolMOS und SiC-JFET in einer hartschaltenden Hochfrequenz-PFC-Stufe (f=1MHz)

### 2.1.1 Grundlagen des Vergleichs

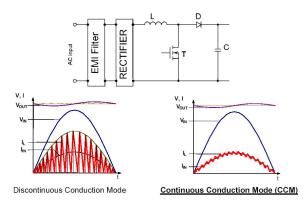

Die Verwendung von aktiven PFC-Stufen ist heutzutage in konventionellen Schaltnetzteilen des höheren Leistungsbereiches, z.B. in Serverapplikationen, Standard. Die Verwendung von Si-MOSFETs als aktive Schalter (T) und Si-Dioden (D) in einer Hochsetzstelleranordnung wurde lange Zeit für im "Discontinuous Conduction Mode" (DCM) betriebene PFC-Stufen eingesetzt (siehe **Bild 18**). Der nächste Schritt zur Erzielung einer höheren Leistung führte zur Verwendung von Si-MOSFETs (T) und SiC-SBD (D).

**Bild 18** Hochsetzsteller PFC-Stufe und ihre Betriebsmodi /5/

Diese Bauelementekombination arbeitet im "Continous Conduction Mode" (CCM) (siehe **Bild 18**). Stand der Technik im oberen Leistungsbereich (Schaltnetzteile bis 3kW) sind heutzutage CCM-PFC-Stufen mit Schaltfrequenzen von ca. 100kHz. Die Senkung der Systemkosten sowie die Erhöhung der Leistungsdichte kann durch eine Verkleinerung der passiven Komponenten erreicht werden. Dies ist wiederum mit einer Erhöhung der Schaltfrequenz verbunden, was durch die Anwendung von SiC-Devices bis in den MHz-Bereich möglich ist. Bei den nachfolgenden Betrachtungen wurde ein rechnerischer

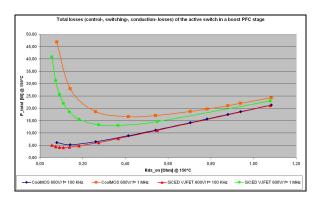

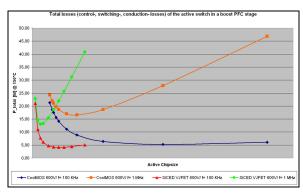

Verlustvergleich beim Einsatz eines 600V-Si-MOSFETs von Infineon und eines SiCED 600V-SiC-VJFET in einer hartschaltenden PFC-Stufe durchgeführt. Folgende Spezifikationen lagen der Berechnung zugrunde: Eingangsleistung 500W, Zwischenkreisspannung 400V, Weitbereichseingangsspannung ≥90V. Die Betrachtungen mussten auf eine maximale Sperrschichttemperatur von T<sub>i</sub>=150°C beschränkt bleiben, da dies die maximal spezifizierte Temperatur für ein Si-MOSFET ist. Die Ansteuerunterschiede zwischen MOSFET und JFET aufgrund des "Normally-off"- bzw. "Normally-on"-Verhaltens sollen bei den Betrachtungen vernachlässigt werden. Verschiedene Treiber-Schutz-Konzepte würden den Betrieb des jeweiligen Schalters ermöglichen. Bei den Berechnungen wurden die Ansteuerverluste, die im Gatewiderstand entstehen, mit berücksichtigt. Die Durchlassverluste, die sich durch den R<sub>DSon</sub> ergeben, sind ein weiterer Teil der Berechnung. Der Anteil der Schaltverluste an den Gesamtverlusten wurde lediglich über die Umladungsverluste der Ausgangskapazität Coss abgeschätzt. Bei dieser Betrachtung wird davon ausgegangen, dass der Kanal des Bauelementes unendlich schnell geschlossen wird und der Strom nur über die Kapazität fließt. Die erzielten Ergebnisse werden nachfolgend dargestellt.

### 2.1.2 Ergebnisse des Vergleichs

Die Resultate der Berechnung für den Verlustleistungsvergleich zwischen 600V Si-CoolMOS und 600V SiC-VJFET bei der geringen Schaltfrequenz f=100kHz und der hohen Schaltfrequenz f=1MHz sind in Bild 19 zu sehen. Es ist zu erkennen, dass bei f=100kHz der optimale R<sub>DSon</sub>, bei dem die geringsten Verluste im aktiven Schalter entstehen, sowohl für den Si-CoolMOS als auch für den SiC-JFET um 100mΩ liegt. Die Verlustkurven für beide Bauelemente liegen bei 100kHz sehr dicht zusammen, sodass noch kein besonderer Vorteil von SiC sichtbar wird. Schaut man hingegen zu der hohen Schaltfrequenz f=1MHz, so ist ein Verlustvorteil vom SiC-Bauelement zu sehen. Der optimale R<sub>DSon</sub> für den JFET ist geringer als der des CoolMOS; er liegt in etwa bei  $300 \text{m}\Omega$  bis  $400 \text{m}\Omega$ . Es ist zu erkennen, dass der Verlustvorteil von SiC mit steigender Temperatur (T>150°C) noch mehr zunimmt. Dies kann mit Hilfe des geringeren positiven Temperaturkoeffizienten des Durchlasswiderstandes von SiC gegenüber dem von Si erklärt werden. Weiterhin ist zu berücksichtigen, dass die Schaltverluste des SiCED VJFET mit steigender Temperatur T<sub>i</sub> abnehmen. Da der JFET einen internen Gatevorwiderstand mit negativen Temperaturkoeffizienten besitzt, nimmt dessen Wert bei hohen Temperaturen ab und der Schaltvorgang wird beschleunigt.

**Bild 19** Verlustleistung gegenüber dem Durchlasswiderstand  $R_{DSon}$  des aktiven Schalters einer Hochsetzsteller-PFC bei  $T_j$ =150°C;  $P_{IN}$ =500W;  $V_{DC}$ =400V;  $V_{IN}$   $_{AC}$ =90V

Dadurch werden Schaltverluste eingespart. Die Darstellung der Verlustleistung im aktiven Bauelement bezogen auf die aktive Chipfläche ist in **Bild 20** zu sehen. Auch in dieser Grafik ist der Verlustleistungsvorteil von SiC gegenüber Si im hohen Frequenzbereich zu erkennen. Beim direkten Vergleich der benötigten aktiven Chipfläche ist zu bemerken, dass diese bei einem SiC-JFET bedeutend kleiner ist als bei einem Si-MOSFET.

Der angeführte Vergleich bietet die Möglichkeit einer Abschätzung der Verluste im aktiven Schalter der PFC-Stufe. Aufgrund der nur teilweise berücksichtigten Schaltverluste sind die abgetragenen Verlustleistungen lediglich als Richtgrößen zu werten, die das Verhältnis zwischen Si- und SiC-Devices widerspiegeln und das Potential von SiC darstellen sollen.

Neben dieser rechnerisch untersuchten Applikation einer Hochfrequenz-PFC-Stufe mit SiC-JFET und SiC-Diode gibt es eine Reihe von Anwendungen, die bereits mit SiC-Bauelementen realisiert werden. Einige Beispiele aus der Schaltnetzteiltechnik werden nachfolgend vorgestellt.

## 2.2 Praktisch realisierte Applikationen mit SiC-Bauelementen

## 2.2.1 Anwendung von SiC-SBD in PFC-Stufen

Die Verwendung von SiC-Dioden in Kombination mit Si-MOSFETs (z.B. CoolMOS) hat sich bei der Realisierung von PFC-Stufen im hohen Leistungsbereich (P=500W bis 3kW) weitgehend durchgesetzt. Im Folgenden werden zwei verschiedene PFC-Stufen vorgestellt.

### 2.2.1.1 Bridgeless-PFC

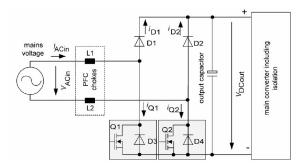

Bei der Bridgeless-PFC handelt es sich um eine Hochsetzsteller-PFC-Stufe, die ohne die Verwendung eines Eingangsgleichrichters arbeitet (siehe **Bild 21**). Durch den zusätzlichen Einsatz eines zweiten Si-MOSFET und einer zweiten SiC-Diode wird neben dem PFC-

Bild 21 Prinzipschaltplan der Bridgeless PFC /5/

Zweig für die positive Netzspannungshalbwelle ein weiterer Zweig für die negative Netzhalbwelle geschaffen. Im Vergleich zu einer konventionellen Hochsetzsteller-PFC wird der verlustbehaftete Brückengleichrichter am PFC-Eingang eingespart.

Bild 22 Bridgeless PFC Demoboard /5/

Für weiterführende Untersuchungen wurde ein Demoboard (siehe **Bild 22**) mit einer Ausgangsleistung von  $P_{OUT}$ =1,5kW realisiert. Es arbeitet bei einer Eingangsspannung im Bereich von  $U_{IN}$ =207V bis  $264V_{ACrms}$  und einer Schaltfrequenz von  $f_S$ =130kHz.

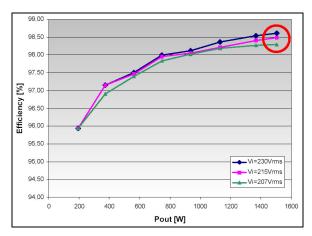

Die erzeugte Zwischenkreisspannung ( $V_{DC}$ ) beträgt 380V. Das Ziel der Applikation war es, einen sehr hohen Wirkungsgrad nahe 99% zu erreichen. Wie an den Ergebnissen der Messungen in **Bild 23** zu sehen ist, wurde diese Vorgabe sehr gut erfüllt.

Bild 23 Wirkungsgrad der Bridgeless PFC-Stufe bei  $f_S$ =130kHz,  $V_{DC}$ =380V /5/

### 2.2.1.2 Boost-PFC

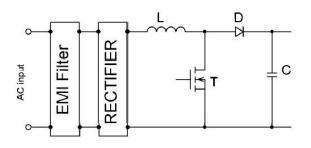

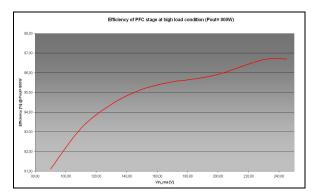

Die Boost-PFC verwendet einen konventionellen Hochsetzsteller mit Eingangsgleichrichter, um den Leistungsfaktor der angeschlossenen Last zu korrigieren. Die Schaltung ist in der heutigen Schaltnetzteil-Applikation weit verbreitet (siehe Bild 24). Für praktische Untersuchungen wurde eine Hochsetzsteller-PFC mit einer Ausgangsleistung  $P_{\rm OUT}$ =800W realisiert. Diese Stufe verwendet einen Si-CoolMOS in Kombination mit einer SiC-SBD. Der Eingangsspannungsbereich ( $U_{\rm IN}$ ) liegt zwischen 90V und 264V $_{\rm ACrms}$ . Er ist somit nicht beschränkt und geht bis in den "Low Line"-Bereich (90V $_{\rm ACrms}$ ). Um die PFC-Drossel im Volumen zu reduzieren, wurde eine Schaltfrequenz von f $_{\rm S}$ =250kHz realisiert.

Bild 24 Prinzipschaltung der Boost PFC /5/

Das Ziel des Aufbaus war es, eine PFC-Stufe zu realisieren, die bei der Verwendung von wenigen Komponenten einen hohen Wirkungsgrad aufweist (siehe **Bild 25**). Der Einsatz von SiC-Dioden ist nicht nur auf PFC-Stufen beschränkt. Auch der Betrieb in einer

**Bild 25** Wirkungsgrad der Boost PFC-Stufe be  $P_{OUT}$ =800W,  $f_S$ =250kHz,  $V_{DC}$ =410V /5/

Hochvolt-Tiefsetzstelleranwendung ist ein interessantes Anwendungsfeld. Auf dieses wird im nächsten Abschnitt näher eingegangen.

### 2.2.2 Applikation von SiC-SBD in Hochvolt-Tiefsetzstelleranordnungen

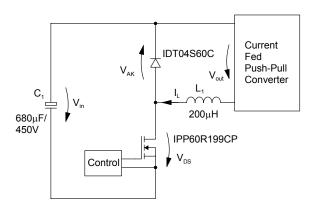

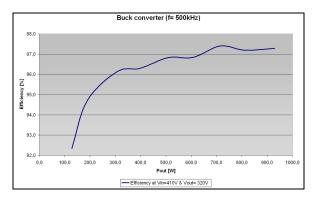

Folgenden dargestellte Hochvolt-Tiefsetzsteller (siehe Bild 26) ist Teil eines Schaltnetzteiles und realisiert dessen Leistungsstellung. Der ihm nachgeschaltete Push-Pull-Konverter übernimmt die Leistungsübertragung zur Sekundärseite eines Transformators, wo durch Gleichrichtung eine 12V-Spannung bereitgestellt wird. Der Tiefsetzsteller wurde mit einem Si-CoolMOS als aktiver Schalter und einer SiC-SBD bestückt. Er arbeitet in einem Eingangsspannungsbereich von 350V bis 410V. Es sind Tastverhältnisse bis maximal 96% möglich. Die Schaltfrequenz beträgt f<sub>s</sub>=500kHz, was die Größe der Tiefsetzstellerdrossel (L<sub>1</sub>) beachtlich reduziert. Der Wirkungsgrad der Applikation ist im Bild 27 zu

Bild 26 Tiefsetzsteller mit SiC-SBD

sehen. Seine Werte liegen bei maximaler Ausgangsleistung (800W) oberhalb von 97%. Die Verwendung von SiC-Dioden in Tiefsetzstelleranwendungen ist besonders für Applikationen mit hohen Spannungen ( $V_{DC}$ =400V) und hohen Strömen geeignet, um das volle Potential der Diode auszuschöpfen. Die bisher vorgestellten Applikationen verwendeten

**Bild 27** Wirkungsgrad des Tiefsetzstellers bei  $V_{IN}$ =410V,  $V_{OUT}$ =320V,  $f_S$ =500kHz

ausschließlich Dioden aus dem Material SiC. Im nachfolgenden Abschnitt wird eine weitere Anwendung vorgestellt, bei der sowohl SiC-SBD als auch SiC-VJFET-Kaskoden in einer Tießetzstelleranwendung zum Einsatz kommen.

### 2.2.3 Applikation von SiC-SBD und SiC-JFET-Kaskoden in einer Hochvolt-Tiefsetzstelleranordnung

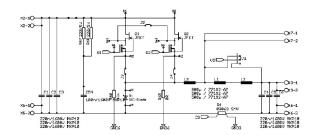

Der Einsatz von sowohl aktiven als auch passiven SiC-Bauelementen in einer Tiefsetzstelleranordnung soll das Potential von Silizium-Karbid zeigen. In der vorgestellten Applikation (siehe **Bild 28**) ist ein Hochvolt-, Hochfrequenz-Tiefsetzsteller mit einer Leistung von P<sub>OUT</sub>=3kW realisiert worden.

Bild 28 Schaltplan des 3kW SiC-Tiefsetzstellers /5/

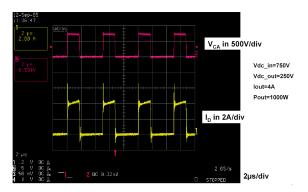

Bei der Topologie handelt es sich um einen "Highside"-Tiefsetzsteller. Als "High-side"-Schalter kam eine SiCED SiC-VJFET-Kaskode (1200V/ 5A/ 0,5Ω) zum Einsatz. Als "Low side"-Schalter diente eine SiC-SBD (1200V). Durch die Verwendung der JFET-Kaskode ist ein "Normally-off"-SiC-Bauelement vorhanden, was mittels konventioneller Treiberschaltung angesteuert werden kann. Der Eingangsspannungsbereich des Konverters ist zwischen 0 und 750V variabel. Die Ausgangsspannung kann zwischen 0 und 700V verändert werden. Als maximaler Ausgangsstrom wurden 4,5A<sub>DC</sub> spezifiziert. Die Schaltfrequenz bei der hartschaltenden Topologie beträgt f<sub>s</sub>=200kHz. Durch die Verwendung der SiC-JFET-Kaskode erleidet man aufgrund des eingesetzten Kaskoden-MOSFETs Einbußen bei der Steuerbarkeit des JFET. Bei der Parallelschaltung von SiC-JFET-Kaskoden existieren einige Problemstellungen bezüglich der Symmetrie und dem Schwingungsverhalten. In **Bild 30** ist das Demoboard, an dem Messungen (siehe **Bild 29**) durchgeführt wurden, zu sehen.

**Bild 29** Schaltvorgänge des 3kW SiC-Tiefsetzstellers bei  $f_S$ =200kHz,  $P_{OUT}$ =1000W,  $I_{OUT}$ =4A Ch1:  $I_D$  (SiC-JFET) Ch2:  $V_{CA}$  (SiC-SBD)

Bild 30 3kW SiC-Tiefsetzstellers Demoboard /5/

Das 3kW SiC-Tiefsetzsteller Demoboard wies einen Wirkungsgrad von mehr als 97% auf. Der Unterschied zu einem Tiefsetzsteller mit Si-CoolMOS und SiC-SBD ist sehr gering. Der Vorteil des SiC-Tiefsetzstellers liegt jedoch in der Anwendbarkeit auch bei hohen Spannungen bzw. bei hohen Temperaturen.

### 3 Literatur

- [1] Friedrichs, P.; Rupp, R.: Silicon Carbide Power Devices-Current Developments and Potential Applications; EPE, 2005

- [2] Rupp, R.: SiC User Forum-Potential of SiC in Power Electronic Applications; ECPE Seminar

- [3] Friedrichs, P.: SiC User Forum-Potential of SiC in Power Electronic Applications; ECPE Seminar 2006

- [4] Mitlehner, H.; Friedrichs, P.; Elpelt, R.; Dohnke, K. O.; Schörner, R.; Stephani, D.:BIFET-a novel bipolar SiC switch for high voltage power electronics; Mat. Science Forum Vols. 457-460(2004) pp.1245-1248

- Reimann, T.: SiC User Forum-Potential of SiC in Power Electronic Applications; ECPE Seminar 2006

### 4 Autoren

Dipl.-Ing. Ulf Schwalbe Dr.-Ing. Tobias Reimann

ISLE Steuerungstechnik und Leistungselektronik GmbH Werner-von-Siemens-Str. 16 D-98693 Ilmenau Germany

Tel. ++49 3677 46 13 0 ++49 3677 46 13 90

Email: u.schwalbe@isle-ilmenau.de

t.reimann@isle-ilmenau.de